Tuesday, August 28th 2012

AMD CTO Mark Papermaster Outlines Vision for 'Surround Computing'

In a keynote address opening the prestigious annual Hot Chips symposium, AMD CTO Mark Papermaster delivered a vision for the coming "Surround Computing Era", and unveiled new processor architecture details, enabling technologies and design methodologies that will help drive the next era in computing. Surround computing is an extension of pervasive and ambient computing trends and describes an environment where computing technologies are completely natural and seamless parts of daily life.

"Surround computing imagines a world without keyboards or mice, where natural user interfaces based on voice and facial recognition redefine the PC experience, and where the cloud and clients collaborate to synthesize exabytes of image and natural language data. The ultimate goal is devices that deliver intelligent, relevant, contextual insight and value that improves consumers' everyday life in real time through a variety of futuristic applications. AMD is leading the quest for devices that understand and anticipate users' needs, are driven by natural user interfaces, and that disappear seamlessly into the background," said Papermaster during his opening remarks.

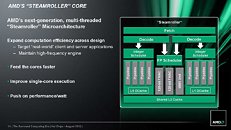

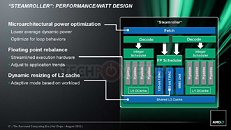

Papermaster explained that the Surround Computing Era will rely on robust "plug-and-play" IP portfolios including central processing units (CPUs), graphics processing units (GPUs), fixed function logic, and interconnect fabric. He also unveiled key details of AMD's upcoming "Steamroller" CPU architecture while underscoring the benefits of the industry-standard Heterogeneous Systems Architecture (HSA) that enables software developers to easily assign scalar and parallel compute workloads to the most appropriate compute units, and therefore optimize power.

"The road that leads us to the Surround Computing Era will be no less challenging and every bit as exciting as the 20-year journey in graphics processing that brought gamers from 'Pong' to today's modern game titles that feature stunning visual realism," Papermaster explained. "It will take an industry movement to complete this journey, and HSA provides the clear path forward to enable this next generation in computing."

"Surround computing imagines a world without keyboards or mice, where natural user interfaces based on voice and facial recognition redefine the PC experience, and where the cloud and clients collaborate to synthesize exabytes of image and natural language data. The ultimate goal is devices that deliver intelligent, relevant, contextual insight and value that improves consumers' everyday life in real time through a variety of futuristic applications. AMD is leading the quest for devices that understand and anticipate users' needs, are driven by natural user interfaces, and that disappear seamlessly into the background," said Papermaster during his opening remarks.

Papermaster explained that the Surround Computing Era will rely on robust "plug-and-play" IP portfolios including central processing units (CPUs), graphics processing units (GPUs), fixed function logic, and interconnect fabric. He also unveiled key details of AMD's upcoming "Steamroller" CPU architecture while underscoring the benefits of the industry-standard Heterogeneous Systems Architecture (HSA) that enables software developers to easily assign scalar and parallel compute workloads to the most appropriate compute units, and therefore optimize power.

"The road that leads us to the Surround Computing Era will be no less challenging and every bit as exciting as the 20-year journey in graphics processing that brought gamers from 'Pong' to today's modern game titles that feature stunning visual realism," Papermaster explained. "It will take an industry movement to complete this journey, and HSA provides the clear path forward to enable this next generation in computing."

22 Comments on AMD CTO Mark Papermaster Outlines Vision for 'Surround Computing'

'Surround Computing'...:rolleyes::wtf:

I like the concept, but again, it is wasted by understating the complexities that we nerds will understand, and overstating the bullshit spin that makes us want to vomit.

I'm not entirely sure that "upgrade friendly" applies to Hudson (FM1 socket) owners either. A year from launch to what is effectively EOL.

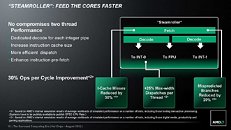

i would expect over 50% improvement from bulldozer to steamroller just based on that

www.techpowerup.com/img/12-08-28/154o.jpg

AMD had an idea, and if it would have happened when Phenom I did, it would have been great, but it didn't instead it has been a slow motion belly flop at the olympics diving competition.

None of their own slides which are marketing and investment seeking mention anything anywhere the 50% mark, 20% I can believe through process improvements, and some tuning of the cores. Is 20% enough? Depends on what 20% they are going to improve, if they think throwing more cores into the mix and the resulting 20% increase is enough they are sadly mistaken. If they are talking about a 20% IPC per core increase on highly dependent branched execution I will applaud them for making it.

trinity is already 15% faster per clock than bulldozer, by what ur saying then ur pretty much saying steamroller will only be 5% faster than piledriver. we all know the biggest bottleneck for bd is the shared front end and with dedicated decoders that problem is solved, so there goes the 20% multithreading scaling penalty and the core starving for resources

So yes 50% over bulldozer or 30% over piledriver is very much likely, that's what is required to put it on par or a bit faster than ivy. But that is based on theory lets hope amd can make it happen. remember 2 cores in bulldozer used 2 share 4 decoders so thats like 2 decoders per core which is pretty wimpy(bobcat has 2 decoders per core)

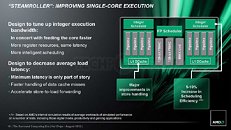

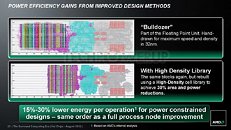

The slides do mention 30% better ops per cycle and 5-10% better efficiency in another slide. But we will wait and see

We all know the biggest bottleneck, who is we, Bulldozer thrives on memory intensive multithreaded applications. It fails hard at single threaded and branching instructions due to mismanaged data scheduling between "cores".

AMD has always been behind in cache hit efficiency, and unless they pull apart a I series and copy it they are not likely to gain too much ground there.

All told I'm sure there might be one benchmark that it is 50% faster at, but in real world situations it is only going to be 20-30%* faster than current design.

*Based on Simulated designs, and simulated workloads done by AMD, of course, for the purpose of keeping their jobs.

I speculate by simulating a simulation of simulations that I will run faster after my morning movement. See how that works, plausible deniability if I don't or they don't since it was based on simulated results obtained from a simulation.

I love the colourful pictures in those slides. :D

TRUE STORY: 5 present AMD board members have held their position since 2006 (i.e. predating BD) back when AMD's board comprised 7 members. AMD just keep adding board members...I think they are up to eleven - nine of which comprise AMD's governance....so, 71% of the deadwood ( the "ridiculous choice makers" as you put it) that signed off on BD still man the helm at the company.

here it is, a couple benchmarks but thats all we have untill piledriver comes out i guess

still piledriver will be atleast 10% faster just due to the stock clock speed which is 4.0ghz, so no need 2 get all pessimistic. as far as i can tell AMD has went a far way in terms of efficiency.

now if anything amd just need 2 get their cores more beefy and it seems thats exactly what they plan to do with steamroller, and if anything they are moving away with wat ruined bulldozer. tho i would argue they sure can benefit from making the pileline shorter. i believe they will keep it at 20 stages. but who knows maybe they plan on doing so with excavator

or maybe sticking to higher clocks was their solution to complement their slower cache subsystem, aslong as they can work around it im good i guess.

I remember too well what Intel tried and it wasn't so much that AMD had superior technology under the hood at the time as much as it was that Intel screwed the pooch. Now we are reversed, AMD keeps trying to spin this flop as if it were somehow great, then they have the balls to try and spin shit they should have been doing 5years ago and alot of us knew it as if it were some rainbow and magic pixie dust idea that no one has ever had before.

Insulting on multiple levels, and to really top it all off, I bet they flop the "fabric" setup and it dies a stillborn death like half of their great ideas.