Sunday, October 13th 2013

AMD "Hawaii" Architecture Diagram Leaked

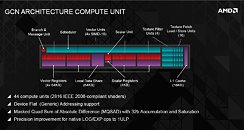

An alleged company slide detailing the architecture of AMD's upcoming "Hawaii" GPU was leaked to the web, revealing a monstrous combination of components. The GPU maintains the same component hierarchy as "Tahiti." The most distinguishing feature here is that whereas "Tahiti" features two shader engines, "Hawaii" features four. What it translates to, is double the geometry processing power, four independent geometry processors with a tessellation unit each, and double the number of ROPs, at 64. Each shader unit features 11 compute units (CU), the number-crunching machinery of the GPU. Each CU holds 4 TMUs (texture memory units), and 64 stream processors.

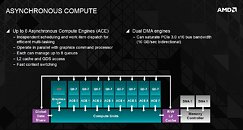

The four shader engines of "Hawaii" are tied to a unified command processing structure, a 1 megabyte L2 cache, a 512-bit wide GDDR5 memory interfaces, and the ancillaries, that include the PCI-Express 3.0 x16 bus interface, six display controllers (six TMDS links in all), CrossFireX XDMA, and multimedia accelerators that include UVD (accelerates high-def video), VCE (video codec engine, accelerates multimedia codecs), and the new TrueAudio hardware DSP.

Source:

3DCenter.org

The four shader engines of "Hawaii" are tied to a unified command processing structure, a 1 megabyte L2 cache, a 512-bit wide GDDR5 memory interfaces, and the ancillaries, that include the PCI-Express 3.0 x16 bus interface, six display controllers (six TMDS links in all), CrossFireX XDMA, and multimedia accelerators that include UVD (accelerates high-def video), VCE (video codec engine, accelerates multimedia codecs), and the new TrueAudio hardware DSP.

17 Comments on AMD "Hawaii" Architecture Diagram Leaked

-=edited=-Don't confusing yourself with your uArch processor :slap:

it explain well you didn't have proper cooling for your own :troll: :nutkick:

If somebody can tell me how a 512 bit memory interface uses less area than a 384 bit one that would be great.

I assume they're talking about the memory interface at the GPU end not the board.

If AMD wasn't rehashing some of the 7x00 series models for this gen then I'd almost think we may finally be coming out of the stagnation period that we've been in since Fermi launched. Not that it has been bad, we've had some great GPUs. But it is about time we moved on.

Its here mostly for compute and yeah its very small, obviously. :)

It kinda makes a bit more sense when given how optimized R9 290X seems to be.

the pcb with the memory controller signals will be much more complicated, crowded and expensive, more than a factor of two, when compared to 256 bit.

512 bit bus width! That's freaking amazing. I wonder how much these will cost!

also 340Kb cache per Cu compute unit makes for a lot of on die cache x44

2816 SP's at a clock speed of ??? (maybe 1050)

64 ROP's

176 TMU's

A Bus that is capable of 64 bytes (512 bits) in a single clock, and does 5 billion clocks in a second moving a substantial 320 Gigabytes in that second

Finally a pool of 4GB VRAM, wow :rockout:

Shaping up to be an amazing card, less TMU's then a GK110 based product though.

I noticed Crysis, Crysis Warhead really likes higher pixel fillrates.

And from what saw higher TMU's matter only at higher resolution or multi monitor setup