Monday, May 25th 2015

Intel's Post-2017 "Purley" Enterprise Platform Detailed

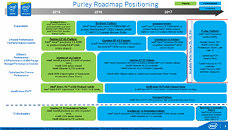

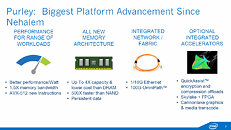

Intel's future enterprise computing business, post-2017, could see a unification of its 2-socket (2S), 4-socket (4S), and >8-socket (8S+) platforms unify into one, codenamed "Purley." The platform will consist of multiple SKUs, but a common socket type (Socket-P), and a new interconnect technology replacing InfiniBand, which will wire the sockets and core-logic across multiple server blades, together. Called Omni-Path Interconnect, the tech appears to be fiber-optic at the physical layer, with extremely thin cables, and bandwidths could start at 100 Gbps, for the first generation. The controller driving it will be codenamed "Storm Lake." The inter-socket communication will be care of a newer 10.4 GT/s UPI interconnect, each socket will feature three such UPI channels. The platform will support up to eight sockets per blade, with more sockets across neighboring blades over Omni-Path.

"Purley" will feature a new platform core-logic, in the form of the "Lewisburg" PCH. It will feature the new DMI3 chipset-bus, which is PCI-Express 3.0 x4 at the physical layer. This chipset will support up to four 10 GbE interfaces. On the processor front, will be as processors based on the "Skylake" micro-architecture. Intel will carve out several silicons based on "Skylake," the biggest one will feature 28 physical CPU cores, with HyperThreading enabling 56 logical CPUs, and for the first time, a six-channel (384-bit wide) DDR4 integrated memory controller, with support for DDR4-2666. On the flip side, this IMC only supports one DIMM per channel (DPC). The 3DPC support from previous platforms is gone. These chips will be built on the 14 nm silicon fab process, and their TDP will range between 45W and 165W, depending on the number of cores and clock speeds.

Source:

AnandTech Forums

"Purley" will feature a new platform core-logic, in the form of the "Lewisburg" PCH. It will feature the new DMI3 chipset-bus, which is PCI-Express 3.0 x4 at the physical layer. This chipset will support up to four 10 GbE interfaces. On the processor front, will be as processors based on the "Skylake" micro-architecture. Intel will carve out several silicons based on "Skylake," the biggest one will feature 28 physical CPU cores, with HyperThreading enabling 56 logical CPUs, and for the first time, a six-channel (384-bit wide) DDR4 integrated memory controller, with support for DDR4-2666. On the flip side, this IMC only supports one DIMM per channel (DPC). The 3DPC support from previous platforms is gone. These chips will be built on the 14 nm silicon fab process, and their TDP will range between 45W and 165W, depending on the number of cores and clock speeds.

7 Comments on Intel's Post-2017 "Purley" Enterprise Platform Detailed