Huawei Reportedly Develops Chip Design Tools for 14 nm and Above

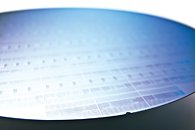

Amid the US sanctions, Chinese technology giant Huawei has reportedly developed tools to create processors with 14 nm and above lithography. According to Chinese media Yicai, Huawei and its semiconductor partners have teamed up to create replacement tools in place of US chip toolmakers like Cadence, Synopsys, and Mentor/Siemens. These three companies control all of the world's Electronic Design Automation (EDA) tools used for every step of chip design, from architecture to placement and routing to the final physical layout. Many steps need to be taken before making a tapeout of a physical chip, and Huawei's newly developed EDA tools will help the Chinese industry with US sanctions which crippled Huawei for a long time.

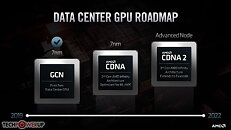

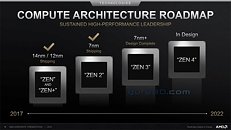

Having no access to US-made chipmaking tools, Huawei has invested substantial time into making these EDA tools. However, with competing EDA makers supporting lithography way below 14 nm, Huawei's job still needs to be completed. Chinese semiconductor factories are currently capable of 7 nm chip production, and Huawei itself is working on making a sub-7 nm EUV scanner to aid manufacturing goals and compete with the latest from TSMC and other. If Huawei can create EUV scanners that can achieve transistor sizes smaller than 7 nm, we expect to see their EDA tools keep pace as well. It is only a matter of time before they announce adaptation for smaller nodes.

Having no access to US-made chipmaking tools, Huawei has invested substantial time into making these EDA tools. However, with competing EDA makers supporting lithography way below 14 nm, Huawei's job still needs to be completed. Chinese semiconductor factories are currently capable of 7 nm chip production, and Huawei itself is working on making a sub-7 nm EUV scanner to aid manufacturing goals and compete with the latest from TSMC and other. If Huawei can create EUV scanners that can achieve transistor sizes smaller than 7 nm, we expect to see their EDA tools keep pace as well. It is only a matter of time before they announce adaptation for smaller nodes.