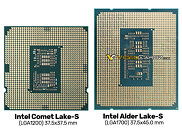

Intel Alder Lake-S CPU Has Been Pictured

Intel has been preparing the launch of its 10 nm processors for desktop users for some time now, and today we are getting the first pictures of the Alder Lake-S CPU backside. Featuring a package with a size of 37.5×45 mm, the Alder Lake CPU uses more of its area for a pin count increase. Going up from 1200 pins in the LGA1200 socket, the new Alder Lake-S CPU uses 1700 CPU pins, which slots in the LGA1700 socket. In the picture below, there is an engineering sample of the Alder Lake-S CPU, which we see for the first time. While there is no much information about the processor, we know that it will use Intel's 10 nm SuperFin design, paired with hybrid core technology. That means that there will be big (Golden Cove) and little (Gracemont) cores in the design. Other features such as PCIe 5.0 and DDR5 should be present as well. The new CPU generation and LGA1700 motherboards are scheduled to arrive in second half of 2021.