Cadence Achieves PCIe 5.0 Specification Compliance for PHY and Controller IP in TSMC Advanced Technologies

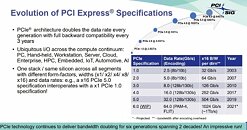

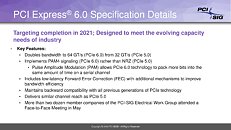

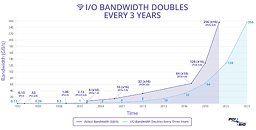

Cadence Design Systems, Inc. (Nasdaq: CDNS) today announced that its PHY and Controller IP for the PCI Express (PCIe ) 5.0 specification in the TSMC N7, N6 and N5 process technologies have passed certification tests from PCI-SIG at the industry's first event for PCIe 5.0 specification compliance held in April. The Cadence solutions were tested to their full potential and complied with the full speed of 32GT/s for PCIe 5.0 technology. The compliance program provides designers with testing procedures to assess that the PCIe 5.0 interfaces on their system-on-chip (SoC) designs will operate as expected.

The Cadence IP for PCIe 5.0 technology consists of a PHY, companion controller and Verification IP (VIP) targeted at SoC designs for very high-bandwidth hyperscale computing, networking and storage applications. With Cadence's PHY and Controller Subsystem for PCIe 5.0 architecture, customers can design extremely power-efficient SoCs while accelerating time to market.

The Cadence IP for PCIe 5.0 technology consists of a PHY, companion controller and Verification IP (VIP) targeted at SoC designs for very high-bandwidth hyperscale computing, networking and storage applications. With Cadence's PHY and Controller Subsystem for PCIe 5.0 architecture, customers can design extremely power-efficient SoCs while accelerating time to market.