KIOXIA CD7 Series PCIe 5.0 SSDs Belt Out 14 GBps Sequential Transfers

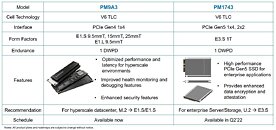

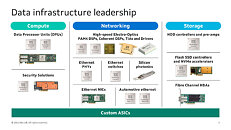

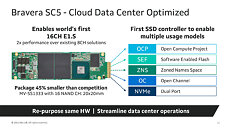

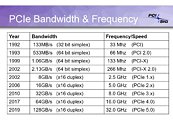

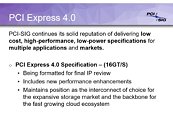

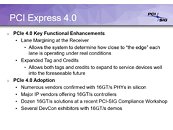

Presenting at the China Flash-Market Summit, KIOXIA unveiled its plans to leverage PCI-Express 5.0 to double SSD performance over the current generation. In typical 4-lane U.2 and M.2 connections, PCI-Express Gen 5 enables an interface bandwidth of 16 GB/s per direction (comparable to PCI-Express 3.0 x16). This means that accounting for interface overheads, typical PCIe Gen 5 SSDs will dance around the 11-15 GB/s (sequential) range. KIOXIA unveiled the CD7, a prototype enterprise SSD in the 2.5-inch EDSFF E3S form-factor with U.2 PCI-Express 5.0 x4 interface. This drive, the company claims, offers up to 14 GB/s sequential transfers, more than double the performance of the current CM6 series drives that leverage PCI-Express Gen 4.

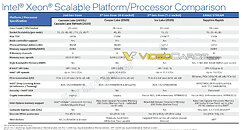

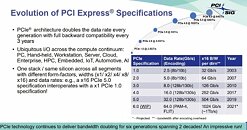

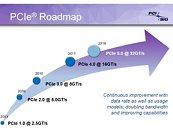

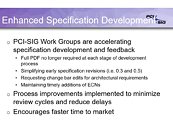

KIOXIA said that its first PCI-Express Gen 5 SSDs will begin shipping in Q4-2021, although it didn't mention if this was mass-market, or to select customers. The first enterprise platforms to leverage Gen 5 won't arrive before mid-2022, with Intel's Xeon "Sapphire Rapids" processors that feature PCI-Express Gen 5 support. KIOXIA sounded optimistic about the future growth in performance of SSDs. "Today, Moore's Law is technically dead in both the CPU and DRAM, but it still works at the PCIe clock rate," the company said, adding ""2015 [was] be the third generation of PCIe, 2019 is the fourth generation, and 2022 will be the fifth generation. Even if people spend a lot of money, they can't double CPU nodes to improve system performance, but buying Gen 5 SSD instead of Gen 4 SSD can greatly improve system performance."

KIOXIA said that its first PCI-Express Gen 5 SSDs will begin shipping in Q4-2021, although it didn't mention if this was mass-market, or to select customers. The first enterprise platforms to leverage Gen 5 won't arrive before mid-2022, with Intel's Xeon "Sapphire Rapids" processors that feature PCI-Express Gen 5 support. KIOXIA sounded optimistic about the future growth in performance of SSDs. "Today, Moore's Law is technically dead in both the CPU and DRAM, but it still works at the PCIe clock rate," the company said, adding ""2015 [was] be the third generation of PCIe, 2019 is the fourth generation, and 2022 will be the fifth generation. Even if people spend a lot of money, they can't double CPU nodes to improve system performance, but buying Gen 5 SSD instead of Gen 4 SSD can greatly improve system performance."