Since the multiplier increment is 0.1 on Zen 3, every degree does matter, as mentioned, even more than on Zen 2. For water-cooling, Conductonaut really makes a lot of sense on the 5950X and 5900x, primarily to maximize 1, 2 and 3 threaded workloads.

Past 3, the heat is actually a lot easier to handle because of the reduced voltage applied to reach multicore workload speeds, 5 core loads being easiest to cool.

I've scaled from 39f to 80f water temps testing this on my 5950x, the hardest thing to cool is a 3 thread non-avx workload that isn't hitting TDC/EDC/PPT limits, because it's going to jump straight to max boost bin and coinciding voltage. AVX triggers reduced speed, even when not hitting limits. Similarly, high EDC all core loads that don't hit PPT/TDC ( like ram stability testing) are hard to cool, it sends my 5950x straight 4930 effective clock all core loads at 1.4 volts because the amerage drawn is so low.

If you have a good block, flow, and cooling capacity the all core loads are trivial on the 5950x.

If you can keep the 5950x under 58c in the 3 thread scenario, temperature scaling from 1-3 stops, and effective clocks will bang right up against the allowed boost limit when not using PBO. Many thread obviously keeps scaling down to subzero temperatures as voltage for a given speed can drop.

Adjusting EDC can influence how aggressive PB2 applies boost, the lower the EDC set, the more aggressively PB2 pushes 1-3 thread workloads. This requires adjustment of CO based on EDC. The higher EDC is set the more CO voltage reduction can be used, and the more single core extends the temperature scaling downwards.

The more you raise EDC, the more CO offset can be used and the lower temp scaling goes, meaning cooler criticality increases. That said, there's NO gain over 160 EDC if all other variables are controlled correctly.

PBO CO 160 EDC 150 TDC 250 PPT, +50mhz nets me at 45f water temp:

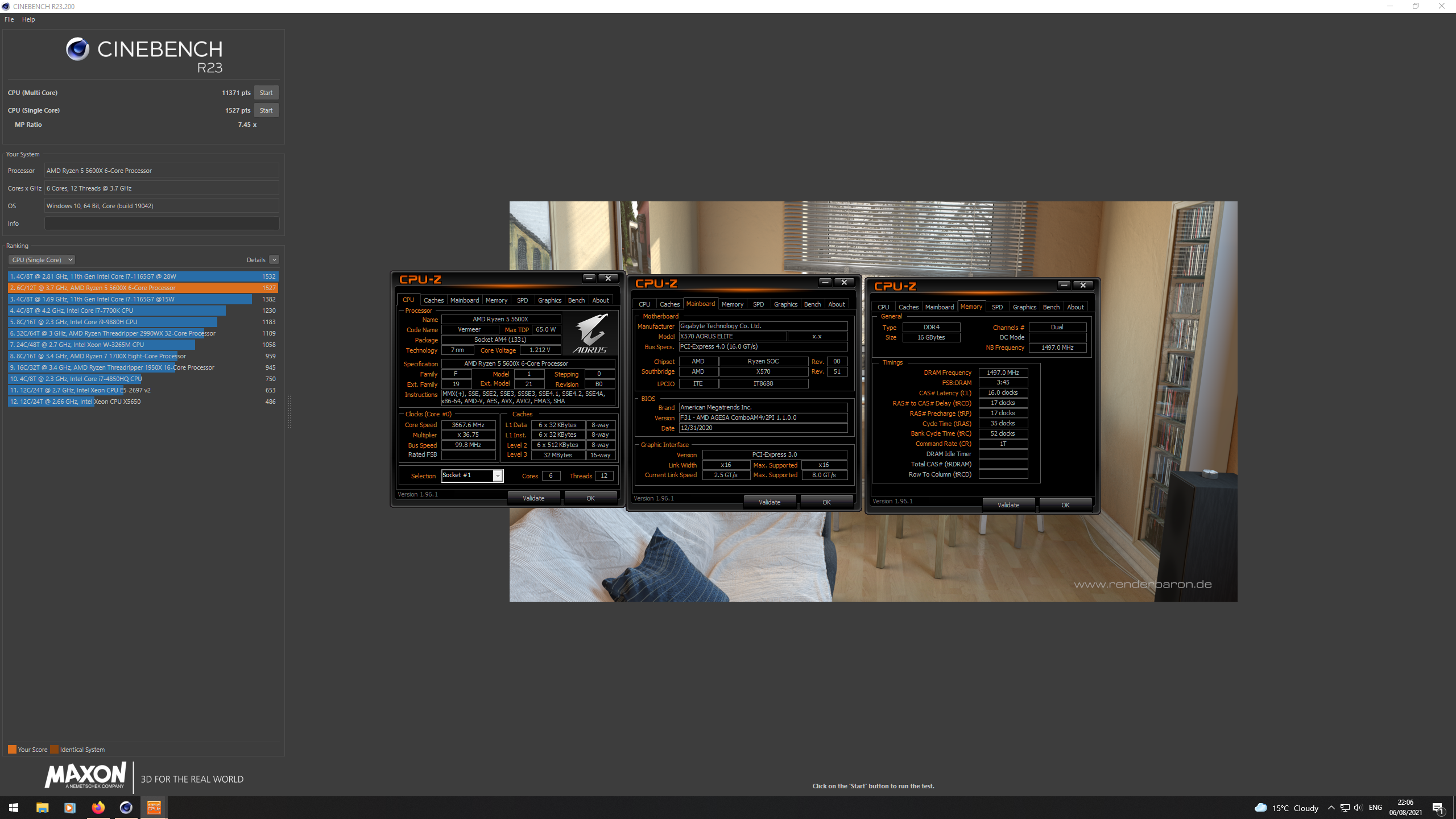

R23 - nT 32550

R23 - sT 1692

Example:

140 EDC 150 TDC 200 PPT, +50 mhz

CO on core 0 at -23

R23 sT - 1671 (5048 effective clock)

Doesn't go any higher once 59f water temps are reached, it is so aggressive it achieves it's limit by 59f water temp.

160 EDC 150 TDC 200 PPT, + 50 mhz

CO on core 0 at -28

R23 sT - 1692 (5093 effective clock)

Scales all the way down to 49f water, 59f water achieves the same scores at 140 EDC, but scaling continues downwards as temp drops.

Also of note, any use of LLC other than auto reduces performance, or if at setting 1 (the most gentle) causes instability(C7H). Auto, as tested by Buildzoid on the C7H, tracks best regarding SET/GET.

Low use crashes/resets were entirely solved by setting the CBS power supply to typical instead of low, using an AX1200i (known good).

Keep in mind, ambient water temps + typical delta will be around 85f. As a result, keeping EDC at 140 and raising TDC to 150-160 and PPT to 200-250 will usually net the best performance paired with as much negative CO as possible, raising the sT scaling of PB2 into the range of use. Lowering EDC to 130 may even help 1-3 thread speeds, haven't tested but the pattern suggests it will. EDC will NOT limit performance when PPT and TDC aren't being limited if CO is tuned if temperature is within what SMU considers acceptable.

PPT should be tuned to hold peak multicore loads at whatever you consider acceptable temps. Doing so will not impact gaming or light/moderate use as all. I tune mine to hold water + 45, which is 250 PPT, holding the CPU at 55c, but very few loads achieve this level of power draw, usually hitting 150 TDC first. R23 draws 225 watts and runs at 4830 mhz at 1.344v GET, hitting TDC and EDC limits, scores do linearly scale with TDC up to 4930 mhz all core at 1.4v GET if I uncap TDC.

1.344v GET I verified using all core OC as manual 4800hz minimum stable voltage, so there's literally nothing to be gained from all core OC vs WELL tuned PBO CO. Lazy PBO CO settings can be beat by all core OC.