- Joined

- Oct 9, 2007

- Messages

- 47,314 (7.52/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

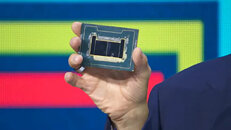

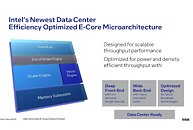

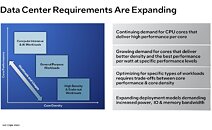

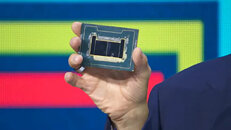

Intel at the 2023 InnovatiON event unveiled a 288-core extreme core-count variant of the Xeon "Sierra Forest" processor for high-density servers for scale-out, cloud-native environments. It succeeds the current 144-core model. "Sierra Forest" is a server processor based entirely on efficiency cores, or E-cores, based on the "Sierra Glen" core microarchitecture, a server-grade derivative of "Crestmont," Intel's second-generation E-core that's making a client debut with "Meteor Lake."

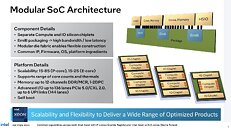

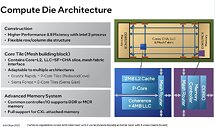

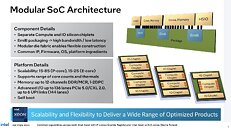

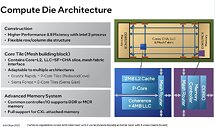

Xeon "Sierra Forest" is a chiplet-based processor, much like "Meteor Lake" and the upcoming "Emerald Rapids" server processor. It features a total of five tiles—two Compute tiles, two I/O tiles, and a base tile (interposer). Each of the two Compute tiles is built on the Intel 3 foundry node, a more advanced node than Intel 4, featuring higher-density libraries, and an undisclosed performance/Watt increase. Each tile has 36 "Sierra Glen" E-core clusters, 108 MB of shared L3 cache, 6-channel (12 sub-channel) DDR5 memory controllers, and Foveros tile-to-tile interfaces.

Each "Sierra Glen" E-core cluster features four CPU cores that share a 4 MB local L2 cache, and a 3 MB segment contributing to the tile's 108 MB L3 cache. Unlike the "Meteor Lake" Compute tile that uses a ringbus to connect its E-core clusters and P-cores, the Compute tile uses a Mesh topology interconnect for the large array of 36 E-core clusters. With 144 cores per tile, in its maximum configuration with three such tiles, "Sierra Forest" achieves 288 cores. "Sierra Glen" lacks SMT, just like "Crestmont," and so the OS only has 288 logical processors to address.

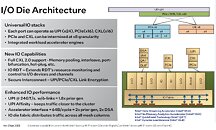

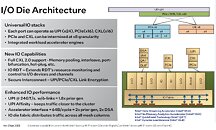

Besides the two Compute tiles, the processor has two I/O tiles. Unlike the similarly named "I/O tile" of the client "Meteor Lake" processor, the ones on "Sierra Forest" serve the functions of both the SoC and I/O PHY. With the memory controllers located on the Compute tiles, in its maximum 288-core variant, "Sierra Forest" features a 12-channel DDR5 memory interface.

The I/O tile is left with the UPI interconnect for 2P servers; application-specific accelerators, a 68-lane PCI-Express Gen 5 root complex that's flexible between PCIe Gen 5 and CXL 2.0, and the I/O Fabric. Despite being based on an advanced node like Intel 3, each of the two Compute tiles is an enormous 578 mm² in die-area, while each of the two I/O tiles is 241 mm².

The up to 12-channel memory interface of "Sierra Forest" comes with native support for ECC DDR5-6400 speed. The accelerators are carried over from the current "Granite Rapids" processor, and provide speed ups for popular cryptography, file-streaming, and and data-compression operations.

When it arrives in the first half of 2024, Xeon "Sierra Forest" will square off against AMD's EPYC "Bergamo" processor. "Bergamo" is based on a slightly different philosophy than "Sierra Forest." It is a 128-core/256-thread processor based on "Zen 4c" cores that don't quite qualify as E-cores, and have an identical IPC to regular "Zen 4" cores, an identical ISA, and SMT.

View at TechPowerUp Main Site | Source

Xeon "Sierra Forest" is a chiplet-based processor, much like "Meteor Lake" and the upcoming "Emerald Rapids" server processor. It features a total of five tiles—two Compute tiles, two I/O tiles, and a base tile (interposer). Each of the two Compute tiles is built on the Intel 3 foundry node, a more advanced node than Intel 4, featuring higher-density libraries, and an undisclosed performance/Watt increase. Each tile has 36 "Sierra Glen" E-core clusters, 108 MB of shared L3 cache, 6-channel (12 sub-channel) DDR5 memory controllers, and Foveros tile-to-tile interfaces.

Each "Sierra Glen" E-core cluster features four CPU cores that share a 4 MB local L2 cache, and a 3 MB segment contributing to the tile's 108 MB L3 cache. Unlike the "Meteor Lake" Compute tile that uses a ringbus to connect its E-core clusters and P-cores, the Compute tile uses a Mesh topology interconnect for the large array of 36 E-core clusters. With 144 cores per tile, in its maximum configuration with three such tiles, "Sierra Forest" achieves 288 cores. "Sierra Glen" lacks SMT, just like "Crestmont," and so the OS only has 288 logical processors to address.

Besides the two Compute tiles, the processor has two I/O tiles. Unlike the similarly named "I/O tile" of the client "Meteor Lake" processor, the ones on "Sierra Forest" serve the functions of both the SoC and I/O PHY. With the memory controllers located on the Compute tiles, in its maximum 288-core variant, "Sierra Forest" features a 12-channel DDR5 memory interface.

The I/O tile is left with the UPI interconnect for 2P servers; application-specific accelerators, a 68-lane PCI-Express Gen 5 root complex that's flexible between PCIe Gen 5 and CXL 2.0, and the I/O Fabric. Despite being based on an advanced node like Intel 3, each of the two Compute tiles is an enormous 578 mm² in die-area, while each of the two I/O tiles is 241 mm².

The up to 12-channel memory interface of "Sierra Forest" comes with native support for ECC DDR5-6400 speed. The accelerators are carried over from the current "Granite Rapids" processor, and provide speed ups for popular cryptography, file-streaming, and and data-compression operations.

When it arrives in the first half of 2024, Xeon "Sierra Forest" will square off against AMD's EPYC "Bergamo" processor. "Bergamo" is based on a slightly different philosophy than "Sierra Forest." It is a 128-core/256-thread processor based on "Zen 4c" cores that don't quite qualify as E-cores, and have an identical IPC to regular "Zen 4" cores, an identical ISA, and SMT.

View at TechPowerUp Main Site | Source