- Joined

- Oct 9, 2007

- Messages

- 47,538 (7.47/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

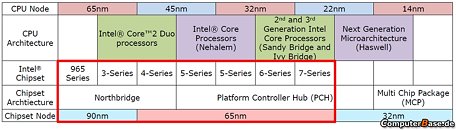

With the 14 nm "Broadwell" architecture, Intel will take a new step towards integration of the platform-controller hub (PCH) with the CPU, by designing it to be a multi-chip module (with the CPU+northbridge in one die, and PCH on the other). This would make "Broadwell" a true System-on-chip (SoC), which allows over 90 percent of the system's I/O to be routed to the processor socket, including memory, PCI-Express, SATA, USB, etc. Although not the first to the industry with single-chip chipsets and integrated memory controllers, Intel rapidly reshaped the arrangement between CPU and core-logic, over the past four years.

It began with transfer of memory controller from northbridge to CPU die (45 nm "Bloomfield"), and transfer of the entire northbridge to the CPU die (45 nm "Lynnfield"). The graphics northbridge transferred a little more gradually, first as multi-chip module with a separate CPU die (32 nm "Clarkdale"), then complete integration with the CPU die (32 nm "Sandy Bridge"). All through, the southbridge, or I/O controller hub (ICH) remained outside the CPU package, with the addition of a display output logic, it transformed into a "platform controller hub" (PCH), which is still just a glorified southbridge. Naturally then, such a drastic relocation of system components will warrant a socket change.

View at TechPowerUp Main Site

It began with transfer of memory controller from northbridge to CPU die (45 nm "Bloomfield"), and transfer of the entire northbridge to the CPU die (45 nm "Lynnfield"). The graphics northbridge transferred a little more gradually, first as multi-chip module with a separate CPU die (32 nm "Clarkdale"), then complete integration with the CPU die (32 nm "Sandy Bridge"). All through, the southbridge, or I/O controller hub (ICH) remained outside the CPU package, with the addition of a display output logic, it transformed into a "platform controller hub" (PCH), which is still just a glorified southbridge. Naturally then, such a drastic relocation of system components will warrant a socket change.

View at TechPowerUp Main Site

Hopefully this will give more room on the motherboard for extra stuff like ram slots, or just make motherboards smaller sense the northbridge will be on chip.

Hopefully this will give more room on the motherboard for extra stuff like ram slots, or just make motherboards smaller sense the northbridge will be on chip.

in the opening headline

in the opening headline