- Joined

- Oct 9, 2007

- Messages

- 47,511 (7.48/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

Intel's next-generation Atom processor platform, codenamed "Bay Trail" doesn't arrive before 2014, but that's not enough to stop the company from talking at great lengths about it. A new presentation intended for Intel's pals in the PC industry was leaked on German tech-forum 3DCenter.org, and reveals quite a bit more about the platform than the Bay Trail-T we already know about.

The first two slides (below) detail key scoring points of the platform over its predecessor, the "Cedar Trail." These include a true single-chip SoC (with complete integration of the chipset into the processor die), being built on the 22 nm Tri-gate transistor fab process, up to four x86-64 cores with out-of-order execution capabilities, 7th generation Intel graphics that features DirectX 11 and supports resolutions as high as 2560 x 1600 pixels, a native USB 3.0 controller, and support for DDR3L memory, that allows device makers to do away with DIMM/SO-DIMM modules to conserve board foot-print, using smaller, space-optimized DRAM chips on the main PCB.

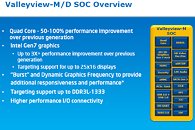

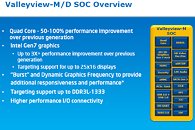

In the third slide, Intel goes into details about the building blocks of the Valleyview SoC, particularly its CPU component. The SoC features up to four 64-bit x86 cores, which support out-of-order execution, the lack of which is a key shortfall of current Atom chips. The introduction of out-of-order execution lends Valleyview's CPU cores a 50~100 percent performance improvement over its previous generation. The cores also feature "Burst," a variation of Turbo Boost that enables higher-clocks in short bursts, rather than throughout high processing loads.

The next key component of the SoC is the 7th generation Intel HD graphics core, which is touted to feature a 300 percent performance improvement over previous-generation, support for the DirectX 11 API, and two TMDS links, supporting display resolutions as high as 2560 x 1600 pixels. Given the pace at which tablet display resolutions are growing, 1600p and 1440p could become commonplace by 2014, and Intel is gearing up for that.

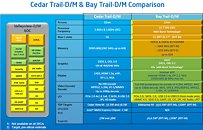

The Bay Trail platform will be classified into three important variations based on target devices, Bay Trail-T for tablets, Bay Trail-M for sub-notebooks, and Bay Trail-D for low-cost desktops, nettops, and set-top boxes. Since tablets are the most space-constrained of the three, Valleyview-T SoC features the smallest package of the lot, measuring 17 x 17 mm, with a target TDP under 3W. To achieve that, it cuts down on pin-count by getting rid of interfaces tablets don't generally feature, such as additional PCIe interfaces, and too many USB ports, while squeezing in room for low-bandwidth low- pin-count interfaces such as SDIO, I2S, HSUART. USB 3.0 OTG finds room.

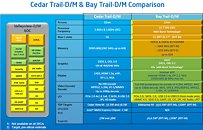

The Bay Trail-M and Bay Trail-D are nearly identical, in featuring a bigger 27 x 25 mm package size, feature-set, support for PC-centric interfaces such as PCI-Express and SATA. The two only differ with Bay Trail-M featuring a TDP target under 6.5W, and Bay Trail-D keeping things relaxed at under 12W. The next slide compares Bay Trail-D/M platforms to their predecessors, the Cedar Trail-D/M.

The last in the slide deck details launch-schedule of Intel's Bay Trail series of platforms. According to it, pre-ES development of the chips will be complete in this quarter for internal testing by Intel, engineering samples fit to be shared by industry partners will be ready by June-August (Q2-Q3), feedback collected will go into making qualification samples (QS) by Q4-2013, and the products will begin rolling out in the first quarter of 2014.

View at TechPowerUp Main Site

The first two slides (below) detail key scoring points of the platform over its predecessor, the "Cedar Trail." These include a true single-chip SoC (with complete integration of the chipset into the processor die), being built on the 22 nm Tri-gate transistor fab process, up to four x86-64 cores with out-of-order execution capabilities, 7th generation Intel graphics that features DirectX 11 and supports resolutions as high as 2560 x 1600 pixels, a native USB 3.0 controller, and support for DDR3L memory, that allows device makers to do away with DIMM/SO-DIMM modules to conserve board foot-print, using smaller, space-optimized DRAM chips on the main PCB.

In the third slide, Intel goes into details about the building blocks of the Valleyview SoC, particularly its CPU component. The SoC features up to four 64-bit x86 cores, which support out-of-order execution, the lack of which is a key shortfall of current Atom chips. The introduction of out-of-order execution lends Valleyview's CPU cores a 50~100 percent performance improvement over its previous generation. The cores also feature "Burst," a variation of Turbo Boost that enables higher-clocks in short bursts, rather than throughout high processing loads.

The next key component of the SoC is the 7th generation Intel HD graphics core, which is touted to feature a 300 percent performance improvement over previous-generation, support for the DirectX 11 API, and two TMDS links, supporting display resolutions as high as 2560 x 1600 pixels. Given the pace at which tablet display resolutions are growing, 1600p and 1440p could become commonplace by 2014, and Intel is gearing up for that.

The Bay Trail platform will be classified into three important variations based on target devices, Bay Trail-T for tablets, Bay Trail-M for sub-notebooks, and Bay Trail-D for low-cost desktops, nettops, and set-top boxes. Since tablets are the most space-constrained of the three, Valleyview-T SoC features the smallest package of the lot, measuring 17 x 17 mm, with a target TDP under 3W. To achieve that, it cuts down on pin-count by getting rid of interfaces tablets don't generally feature, such as additional PCIe interfaces, and too many USB ports, while squeezing in room for low-bandwidth low- pin-count interfaces such as SDIO, I2S, HSUART. USB 3.0 OTG finds room.

The Bay Trail-M and Bay Trail-D are nearly identical, in featuring a bigger 27 x 25 mm package size, feature-set, support for PC-centric interfaces such as PCI-Express and SATA. The two only differ with Bay Trail-M featuring a TDP target under 6.5W, and Bay Trail-D keeping things relaxed at under 12W. The next slide compares Bay Trail-D/M platforms to their predecessors, the Cedar Trail-D/M.

The last in the slide deck details launch-schedule of Intel's Bay Trail series of platforms. According to it, pre-ES development of the chips will be complete in this quarter for internal testing by Intel, engineering samples fit to be shared by industry partners will be ready by June-August (Q2-Q3), feedback collected will go into making qualification samples (QS) by Q4-2013, and the products will begin rolling out in the first quarter of 2014.

View at TechPowerUp Main Site