Raevenlord

News Editor

- Joined

- Aug 12, 2016

- Messages

- 3,755 (1.19/day)

- Location

- Portugal

| System Name | The Ryzening |

|---|---|

| Processor | AMD Ryzen 9 5900X |

| Motherboard | MSI X570 MAG TOMAHAWK |

| Cooling | Lian Li Galahad 360mm AIO |

| Memory | 32 GB G.Skill Trident Z F4-3733 (4x 8 GB) |

| Video Card(s) | Gigabyte RTX 3070 Ti |

| Storage | Boot: Transcend MTE220S 2TB, Kintson A2000 1TB, Seagate Firewolf Pro 14 TB |

| Display(s) | Acer Nitro VG270UP (1440p 144 Hz IPS) |

| Case | Lian Li O11DX Dynamic White |

| Audio Device(s) | iFi Audio Zen DAC |

| Power Supply | Seasonic Focus+ 750 W |

| Mouse | Cooler Master Masterkeys Lite L |

| Keyboard | Cooler Master Masterkeys Lite L |

| Software | Windows 10 x64 |

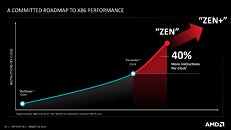

After spending almost 4 years developing and perfecting (as much as can be perfected in such an amount of time) it's ZEN CPU architecture, AMD is looking to extract some mileage out of it. Mark Papermaster, AMD's chief technology officer, confirmed the four-year lifespan in a conversation with PC World at CES 2017 in Las Vegas, though he declined to discuss specifics. When asked how long ZEN would last (especially comparing to Intel's now-failing two-year tick-tock cadence, Papermaster confirmed the four-year lifespan: "We're not going tick-tock," he said. "ZEN is going to be tock, tock, tock."

Intel's tick-tock cadence has typically meant that it develops a new micro-architecture every two years (tock), with a process improvement in-between architectures (the tick). Of these, Kaby Lake is the first exception, ushering in a second "tick" moment for the company, which leveraged what it calls its "14 nm +" manufacturing process. AMD, on the other hand, has typically drawn more than 4 years worth of products from most of its micro-architectures (even Bulldozer has lasted from late 2011 until now), with AMD focusing in incremental updates in-between major architecture launches (such as Bulldozer's Piledriver, Steamroller, and Excavator updates).

On Papermaster's words, it seems AMD is planning to iteratively improve its Ryzen chips through some additional generations - whether at the cadence of their Bulldozer architecture or not, remains to be seen, but it can be expected that that will be the case. What those improvements will be, of course, are for now anyone's guess. But Papermaster also said he's a believer in architecture improvements that go beyond simple manufacturing - something he's previously referred to as "Moore's Law Plus."

In interviews, Mark Papermaster referred to this as the industry's failure to achieve Moore's law through transistor shrinking alone - as had been historically the case. Moore's Law Plus means that chipmakers will have to find creative, less-streamlined ways of inching closer to what Moore's Law (in its Intel's David House coating, who predicted that chip performance would double every 18 months) stipulates. According to Papermaster, "It will be ingenuity at the system level to put solutions together. It might be combinations of CPU and GPU, other accelerators, different memory configurations, how they're pieced together - there's room for lots of innovation at the next level."

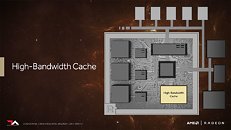

We're actually seeing hints of that with AMD's upcoming VEGA architecture's additions of a High-Bandwidth Cache (HBC) and an High-Bandwidth Cache Controller (HBCC): of which you can have an excellent read right here at TechPowerUp. How this will translate with the CPU side of the equation, and what this means for AMD's ZEN or forthcoming CPU architectures, however, remains to be seen.

View at TechPowerUp Main Site

Intel's tick-tock cadence has typically meant that it develops a new micro-architecture every two years (tock), with a process improvement in-between architectures (the tick). Of these, Kaby Lake is the first exception, ushering in a second "tick" moment for the company, which leveraged what it calls its "14 nm +" manufacturing process. AMD, on the other hand, has typically drawn more than 4 years worth of products from most of its micro-architectures (even Bulldozer has lasted from late 2011 until now), with AMD focusing in incremental updates in-between major architecture launches (such as Bulldozer's Piledriver, Steamroller, and Excavator updates).

On Papermaster's words, it seems AMD is planning to iteratively improve its Ryzen chips through some additional generations - whether at the cadence of their Bulldozer architecture or not, remains to be seen, but it can be expected that that will be the case. What those improvements will be, of course, are for now anyone's guess. But Papermaster also said he's a believer in architecture improvements that go beyond simple manufacturing - something he's previously referred to as "Moore's Law Plus."

In interviews, Mark Papermaster referred to this as the industry's failure to achieve Moore's law through transistor shrinking alone - as had been historically the case. Moore's Law Plus means that chipmakers will have to find creative, less-streamlined ways of inching closer to what Moore's Law (in its Intel's David House coating, who predicted that chip performance would double every 18 months) stipulates. According to Papermaster, "It will be ingenuity at the system level to put solutions together. It might be combinations of CPU and GPU, other accelerators, different memory configurations, how they're pieced together - there's room for lots of innovation at the next level."

We're actually seeing hints of that with AMD's upcoming VEGA architecture's additions of a High-Bandwidth Cache (HBC) and an High-Bandwidth Cache Controller (HBCC): of which you can have an excellent read right here at TechPowerUp. How this will translate with the CPU side of the equation, and what this means for AMD's ZEN or forthcoming CPU architectures, however, remains to be seen.

View at TechPowerUp Main Site