- Joined

- Oct 9, 2007

- Messages

- 47,878 (7.38/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

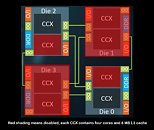

At its pre-launch media conference call for the Ryzen Threadripper 1900X, AMD mentioned that the chip has been carved out from the common 4-die EPYC MCM using a "4-0-4-0 diagonal configuration," which led to some confusion as to which cores/dies AMD disabled to carve out the $549 8-core HEDT processor. The company shed some light on this matter, responding to questions from TechPowerUp.

It turns out, that the Threadripper 1900X features an entire CCX (quad-core CPU complex) disabled per active die on the multi-chip module, so the CCX that's enabled has 8 MB of L3 cache; and access to the die's entire uncore resources, such as the dual-channel memory controller, PCIe root complex, etc. With two such active "Zeppelin" dies, the Threadripper 1900X ends up with 8 cores, 16 MB of L3 cache, a quad-channel memory interface, and 64 PCIe lanes.

The decision to disable an entire CCX, rather than doing something similar to the "Zeppelin" die as with the Ryzen 5 1400, where both CCX units on the die are enabled with 2 cores, each; and the L3 cache per CCX being chopped down to 4 MB; could be attributed to giving the four cores per active CCX a contiguous block of 8 MB L3 cache, to better cushion the NUMA local mode, in which certain applications' memory access can be localized to one die, for lower latency.

When AMD talks about a "diagonal configuration," it refers to the fact that two out of four 8-core "Zeppelin" dies physically present on the Threadripper multi-chip module, are disabled. The ones disabled are always diagonally opposite to each other. The Threadripper MCM is physically identical to the 32-core EPYC MCM, with four 8-core "Zeppelin" dies under its large integrated heatspreader (IHS); but due to platform-segmentation, and the fact that the Threadripper socket TR4 HEDT platform only has 4 memory channels (unlike 8 channels on the EPYC platform); two dies are completely disabled. The dies are disabled diagonally probably to spread heat better, or for better package wiring.

View at TechPowerUp Main Site

It turns out, that the Threadripper 1900X features an entire CCX (quad-core CPU complex) disabled per active die on the multi-chip module, so the CCX that's enabled has 8 MB of L3 cache; and access to the die's entire uncore resources, such as the dual-channel memory controller, PCIe root complex, etc. With two such active "Zeppelin" dies, the Threadripper 1900X ends up with 8 cores, 16 MB of L3 cache, a quad-channel memory interface, and 64 PCIe lanes.

The decision to disable an entire CCX, rather than doing something similar to the "Zeppelin" die as with the Ryzen 5 1400, where both CCX units on the die are enabled with 2 cores, each; and the L3 cache per CCX being chopped down to 4 MB; could be attributed to giving the four cores per active CCX a contiguous block of 8 MB L3 cache, to better cushion the NUMA local mode, in which certain applications' memory access can be localized to one die, for lower latency.

When AMD talks about a "diagonal configuration," it refers to the fact that two out of four 8-core "Zeppelin" dies physically present on the Threadripper multi-chip module, are disabled. The ones disabled are always diagonally opposite to each other. The Threadripper MCM is physically identical to the 32-core EPYC MCM, with four 8-core "Zeppelin" dies under its large integrated heatspreader (IHS); but due to platform-segmentation, and the fact that the Threadripper socket TR4 HEDT platform only has 4 memory channels (unlike 8 channels on the EPYC platform); two dies are completely disabled. The dies are disabled diagonally probably to spread heat better, or for better package wiring.

View at TechPowerUp Main Site

Last edited: