Raevenlord

News Editor

- Joined

- Aug 12, 2016

- Messages

- 3,755 (1.20/day)

- Location

- Portugal

| System Name | The Ryzening |

|---|---|

| Processor | AMD Ryzen 9 5900X |

| Motherboard | MSI X570 MAG TOMAHAWK |

| Cooling | Lian Li Galahad 360mm AIO |

| Memory | 32 GB G.Skill Trident Z F4-3733 (4x 8 GB) |

| Video Card(s) | Gigabyte RTX 3070 Ti |

| Storage | Boot: Transcend MTE220S 2TB, Kintson A2000 1TB, Seagate Firewolf Pro 14 TB |

| Display(s) | Acer Nitro VG270UP (1440p 144 Hz IPS) |

| Case | Lian Li O11DX Dynamic White |

| Audio Device(s) | iFi Audio Zen DAC |

| Power Supply | Seasonic Focus+ 750 W |

| Mouse | Cooler Master Masterkeys Lite L |

| Keyboard | Cooler Master Masterkeys Lite L |

| Software | Windows 10 x64 |

Researchers based on Purdue University have designed an intrachip cooling technology, which will likely pave the way for future generations of high performance 3D microprocessors. The research was part of a DARPA-funded commission for Purdue University's Birck Nanotechnology Center; a fundamental requirement stipulated by DARPA was the ability for this cooling system to handle chips generating 1 kW of heat per cm², more than 10x the amount current high-performance computers generate.

The new cooling system circulates an electrically insulated liquid coolant directly into electronic chips through an intricate series of tiny microchannels. This means that no longer will cooling systems be limited to the nowadays-employed conventional chip-cooling methods, which make use of finned metal plates called heat sinks. These are attached to computer chips to dissipate heat, but have a fundamental flaw: they do not remove heat efficiently enough for an emerging class of high-performance, 3D electronics, where too much heat hinders the performance of electronic chips or damages the tiny circuitry, especially in small "hot spots" that are located below the topmost layer of the chip.

"You can pack only so much computing power into a single chip, so stacking chips on top of each other is one way of increasing performance," said Justin A. Weibel, a research associate professor in Purdue's School of Mechanical Engineering, and co-investigator on the project. "This presents a cooling challenge because if you have layers of many chips, normally each one of these would have its own system attached on top of it to draw out heat. As soon as you have even two chips stacked on top of each other the bottom one has to operate with significantly less power because it can't be cooled directly."

Suresh V. Garimella, who is principal investigator for the project and the Goodson Distinguished Professor of Mechanical Engineering at Purdue University, added that "This transformative approach has great promise for use in radar electronics, as well as in high-performance supercomputers. In this paper, we have demonstrated the technology and the unprecedented performance it provides."

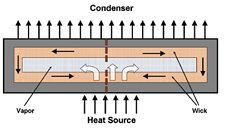

The system uses a commercial refrigerant called HFE-7100, a dielectric, or electrically insulating fluid, meaning it won't cause short circuits in the electronics. As the fluid circulates over the heat source, it boils inside the microchannels, somewhat like current vapor-chamber technology - but multiplied by X.

"Allowing the liquid to boil dramatically increases how much heat can be removed, compared to simply heating a liquid to below its boiling point," said Garimella. To increase efficiency and reduce pressure drops associated with long cooling channels that cover the length of the chip to be cooled, the team opted for a system of short, parallel channels, where a "hierarchical" manifold distributes the flow of coolant. "So, instead of a channel being 5,000 microns in length, we shorten it to 250 microns long," Garimella added. "The total length of the channel is the same, but it is now fed in discrete segments, and this prevents major pressure drops. So this represents a different paradigm."

View at TechPowerUp Main Site

The new cooling system circulates an electrically insulated liquid coolant directly into electronic chips through an intricate series of tiny microchannels. This means that no longer will cooling systems be limited to the nowadays-employed conventional chip-cooling methods, which make use of finned metal plates called heat sinks. These are attached to computer chips to dissipate heat, but have a fundamental flaw: they do not remove heat efficiently enough for an emerging class of high-performance, 3D electronics, where too much heat hinders the performance of electronic chips or damages the tiny circuitry, especially in small "hot spots" that are located below the topmost layer of the chip.

"You can pack only so much computing power into a single chip, so stacking chips on top of each other is one way of increasing performance," said Justin A. Weibel, a research associate professor in Purdue's School of Mechanical Engineering, and co-investigator on the project. "This presents a cooling challenge because if you have layers of many chips, normally each one of these would have its own system attached on top of it to draw out heat. As soon as you have even two chips stacked on top of each other the bottom one has to operate with significantly less power because it can't be cooled directly."

Suresh V. Garimella, who is principal investigator for the project and the Goodson Distinguished Professor of Mechanical Engineering at Purdue University, added that "This transformative approach has great promise for use in radar electronics, as well as in high-performance supercomputers. In this paper, we have demonstrated the technology and the unprecedented performance it provides."

The system uses a commercial refrigerant called HFE-7100, a dielectric, or electrically insulating fluid, meaning it won't cause short circuits in the electronics. As the fluid circulates over the heat source, it boils inside the microchannels, somewhat like current vapor-chamber technology - but multiplied by X.

"Allowing the liquid to boil dramatically increases how much heat can be removed, compared to simply heating a liquid to below its boiling point," said Garimella. To increase efficiency and reduce pressure drops associated with long cooling channels that cover the length of the chip to be cooled, the team opted for a system of short, parallel channels, where a "hierarchical" manifold distributes the flow of coolant. "So, instead of a channel being 5,000 microns in length, we shorten it to 250 microns long," Garimella added. "The total length of the channel is the same, but it is now fed in discrete segments, and this prevents major pressure drops. So this represents a different paradigm."

View at TechPowerUp Main Site