- Joined

- Oct 9, 2007

- Messages

- 47,571 (7.46/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

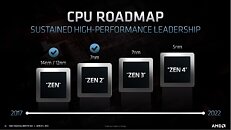

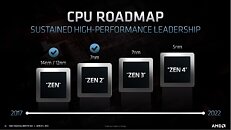

AMD's 4th generation EPYC line of enterprise processors, now into design stage, impressed the United States Department of Energy enough that it wants to deploy it in "El Capitan," a 2 ExaFLOP supercomputer that will be the world's most powerful, when it goes online around 2022. Codenamed "Genoa," 4th gen EPYC implements AMD's "Zen 4" microarchitecture. While AMD didn't get into too many details about it in its 2020 Financial Analyst Day address, there are a couple of details.

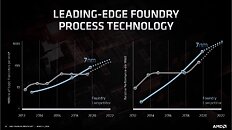

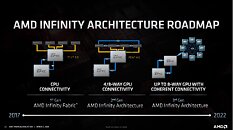

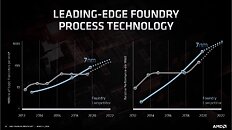

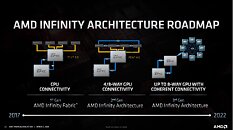

For starters, "Zen 4" continues on AMD's trajectory of adding IPC gains with each generation. Secondly, "Zen 4" will leverage the advanced 5 nm silicon fabrication process, which should significantly increase transistor densities over even the most advanced iterations of 7 nm, such as 7 nm EUV. "Zen 4" comes out roughly the same time as the RDNA3 and CDNA2 graphics architectures, and AMD's 3rd generation Infinity Fabric interconnect that enables exascale supercomputers thanks to coherent unified memory and vast shared memory pools between CPUs and compute GPUs. Elsewhere in the roadmap, we see AMD announcing that its upcoming "Zen 3" microarchitecture and its enterprise implementation, the EPYC "Milan" processor, will release only toward the end of 2020. This would give EPYC "Rome" close to 6 calendar quarters of market leadership.

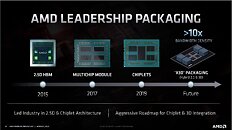

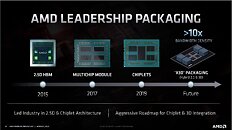

Although not in reference to "Genoa," AMD briefly talked about the next step in its package innovations that have helped it overcome the effects of a slowdown in Moore's Law cadence. The company implemented MCMs for its first-generation "Naples," and transcended to the chiplet approach with second generation "Rome," in which only those components that benefit from the switch to a new node would be built on the new node, while uncore and I/O components would be built on separate dies and older process nodes, which is largely expected to carry forward with "Milan." Some time in the future, through, the company could embrace an X3D "2.5D + 3D" package design that sees the combination of 3D memory stacks sitting alongside 2.5D logic stacks.

View at TechPowerUp Main Site

For starters, "Zen 4" continues on AMD's trajectory of adding IPC gains with each generation. Secondly, "Zen 4" will leverage the advanced 5 nm silicon fabrication process, which should significantly increase transistor densities over even the most advanced iterations of 7 nm, such as 7 nm EUV. "Zen 4" comes out roughly the same time as the RDNA3 and CDNA2 graphics architectures, and AMD's 3rd generation Infinity Fabric interconnect that enables exascale supercomputers thanks to coherent unified memory and vast shared memory pools between CPUs and compute GPUs. Elsewhere in the roadmap, we see AMD announcing that its upcoming "Zen 3" microarchitecture and its enterprise implementation, the EPYC "Milan" processor, will release only toward the end of 2020. This would give EPYC "Rome" close to 6 calendar quarters of market leadership.

Although not in reference to "Genoa," AMD briefly talked about the next step in its package innovations that have helped it overcome the effects of a slowdown in Moore's Law cadence. The company implemented MCMs for its first-generation "Naples," and transcended to the chiplet approach with second generation "Rome," in which only those components that benefit from the switch to a new node would be built on the new node, while uncore and I/O components would be built on separate dies and older process nodes, which is largely expected to carry forward with "Milan." Some time in the future, through, the company could embrace an X3D "2.5D + 3D" package design that sees the combination of 3D memory stacks sitting alongside 2.5D logic stacks.

View at TechPowerUp Main Site