Raevenlord

News Editor

- Joined

- Aug 12, 2016

- Messages

- 3,755 (1.20/day)

- Location

- Portugal

| System Name | The Ryzening |

|---|---|

| Processor | AMD Ryzen 9 5900X |

| Motherboard | MSI X570 MAG TOMAHAWK |

| Cooling | Lian Li Galahad 360mm AIO |

| Memory | 32 GB G.Skill Trident Z F4-3733 (4x 8 GB) |

| Video Card(s) | Gigabyte RTX 3070 Ti |

| Storage | Boot: Transcend MTE220S 2TB, Kintson A2000 1TB, Seagate Firewolf Pro 14 TB |

| Display(s) | Acer Nitro VG270UP (1440p 144 Hz IPS) |

| Case | Lian Li O11DX Dynamic White |

| Audio Device(s) | iFi Audio Zen DAC |

| Power Supply | Seasonic Focus+ 750 W |

| Mouse | Cooler Master Masterkeys Lite L |

| Keyboard | Cooler Master Masterkeys Lite L |

| Software | Windows 10 x64 |

In today's world, fabrication process identification of semiconductor technology has become little more than marketing fluff. Whereas not that long ago, fabrication processes could (mostly) be directly compared on the basis of transistor density (ie, 300 nm, 32 nm, 14 nm, and now 7 nm), recent advances in manufacturing technologies and their end terminology have lost all significance when it comes to actually describe how density that process is. The way manufacturers measured this semiconductor density used to directly refer to the minimum gate length in transistors fabricated in a given process - that, is, in 300 nm, the minimum gate length that could be achieved was 300 nanometers, in 32 nm, 32 nanometres, and so on. As of now, that isn't happening - which is why we've got Intel saying that its 10 nm fabrication process will be comparable to TSMC's current 7 nm process.

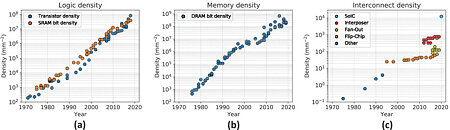

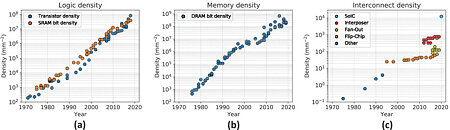

This leads to a number of difficulties for interested parties to actually glean any meaningful information from this particular semiconductor metric alone. Now, a team of researchers has tackled this problem by suggesting a different way to express semiconductor manufacturing capability. Their intention is to allow to "gauge advances in future generations of semiconductor technologies in a holistic way, by accounting for the progress in logic, memory, and packaging/integration technologies simultaneously." As such, their proposed density metric follows a [DL, DM, DC] philosophy, where DL is the density of logic transistors (in #/mm²), DM is the bit density of main memory (currently the off-chip DRAM density, in #/mm²), and DC is the density of connections between the main memory and logic (in #/mm²). The researchers say that current top semiconductor technology density available would be described by this system as [38M, 383M, 12K].

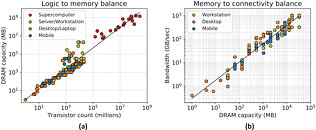

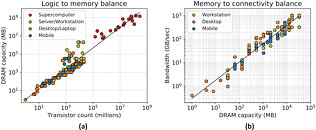

The researchers include metrics such as DM and DC because current computer systems absolutely depend on off-chip memory density, and I/O and actual logic/memory throughput is increasingly important in all computing scenarios (and especially as computing performance increases). Furthermore, the researchers have noted a comparable increase in density of logic transistors and DRAM bit density, which adds to this new density metric. Remember that these values are supposed to represent the maximum effective capability of any given manufacturing process - this means that a next-generation process from Intel could include maximum transistor density expressed in the result of an equation as simple as number of transistors divided by the die area; the maximum available DRAM bit density of memory that can be paired with this fabrication process chip (we expect this number to be changed across product portfolios in a given generation should compatible DRAM density advancements occur in the lifetime of a given die logic manufacturing lifetime; as well as density of logic-to-memory connectivity.

Considering the current naming convention landscape for manufacturing process density is... filled with as many plot-holes as some super-hero franchises, this seems like a sensible way to go about in actually forcing a level playing field between manufacturers. They keep their leeway in marketing terms to describe their processes as they want, but must also provide these density metrics for their process technologies. And since this refers to the maximum densities their process can support (when it comes to transistor logic and memory connection logic densities), it ensures that consumers, institutions, and companies can actually look at the semiconductor landscape with a clear picture.

View at TechPowerUp Main Site

This leads to a number of difficulties for interested parties to actually glean any meaningful information from this particular semiconductor metric alone. Now, a team of researchers has tackled this problem by suggesting a different way to express semiconductor manufacturing capability. Their intention is to allow to "gauge advances in future generations of semiconductor technologies in a holistic way, by accounting for the progress in logic, memory, and packaging/integration technologies simultaneously." As such, their proposed density metric follows a [DL, DM, DC] philosophy, where DL is the density of logic transistors (in #/mm²), DM is the bit density of main memory (currently the off-chip DRAM density, in #/mm²), and DC is the density of connections between the main memory and logic (in #/mm²). The researchers say that current top semiconductor technology density available would be described by this system as [38M, 383M, 12K].

The researchers include metrics such as DM and DC because current computer systems absolutely depend on off-chip memory density, and I/O and actual logic/memory throughput is increasingly important in all computing scenarios (and especially as computing performance increases). Furthermore, the researchers have noted a comparable increase in density of logic transistors and DRAM bit density, which adds to this new density metric. Remember that these values are supposed to represent the maximum effective capability of any given manufacturing process - this means that a next-generation process from Intel could include maximum transistor density expressed in the result of an equation as simple as number of transistors divided by the die area; the maximum available DRAM bit density of memory that can be paired with this fabrication process chip (we expect this number to be changed across product portfolios in a given generation should compatible DRAM density advancements occur in the lifetime of a given die logic manufacturing lifetime; as well as density of logic-to-memory connectivity.

Considering the current naming convention landscape for manufacturing process density is... filled with as many plot-holes as some super-hero franchises, this seems like a sensible way to go about in actually forcing a level playing field between manufacturers. They keep their leeway in marketing terms to describe their processes as they want, but must also provide these density metrics for their process technologies. And since this refers to the maximum densities their process can support (when it comes to transistor logic and memory connection logic densities), it ensures that consumers, institutions, and companies can actually look at the semiconductor landscape with a clear picture.

View at TechPowerUp Main Site