- Joined

- Oct 9, 2007

- Messages

- 47,448 (7.50/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

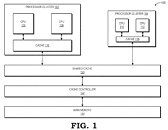

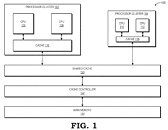

In a sign of AMD's answer to Intel Hybrid tech being quite far away from implementation in a product, the company filed patents to a rival/similar technology only as recently as June 30, 2020, with the patent application being dug up by Underfox. The patent calls for a multi-core processor topology with two kinds of CPU cores - a "high-feature" core (big core), and a "low-feature" one (small core).

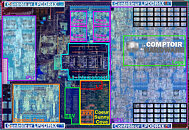

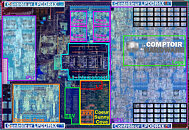

Here's where AMD's design is different: it calls for closely integrated groups of the two kinds of cores (one big core, and one small core), called "Processor Clusters." The dedicated L1 caches of the big and small cores in each group shadow data, while an L2 cache is shared between the two cores. Several such big+small Processor Clusters sit across a die, sharing the chip's last-level cache (L3 cache). This is unlike Intel's Hybrid design, where the big and small cores are spread apart on the die, with little cache coherency (Lakefield die-shot by le Comptoir du Hardware below). The patent also details the workflow of how the processor reconciles the ISA differences between the two core types.

View at TechPowerUp Main Site

Here's where AMD's design is different: it calls for closely integrated groups of the two kinds of cores (one big core, and one small core), called "Processor Clusters." The dedicated L1 caches of the big and small cores in each group shadow data, while an L2 cache is shared between the two cores. Several such big+small Processor Clusters sit across a die, sharing the chip's last-level cache (L3 cache). This is unlike Intel's Hybrid design, where the big and small cores are spread apart on the die, with little cache coherency (Lakefield die-shot by le Comptoir du Hardware below). The patent also details the workflow of how the processor reconciles the ISA differences between the two core types.

View at TechPowerUp Main Site

...

...