- Joined

- Aug 19, 2017

- Messages

- 2,945 (1.05/day)

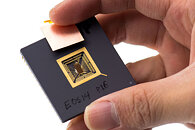

OpenFive, a leading provider of customizable, silicon-focused solutions with differentiated IP, today announced the successful tape out of a high-performance SoC on TSMC's N5 process, with integrated IP solutions targeted for cutting edge High Performance Computing (HPC)/AI, networking, and storage solutions.

The SoC features an OpenFive High Bandwidth Memory (HBM3) IP subsystem and D2D I/Os, as well as a SiFive E76 32-bit CPU core. The HBM3 interface supports 7.2 Gbps speeds allowing high throughput memories to feed domain-specific accelerators in compute-intensive applications including HPC, AI, Networking, and Storage. OpenFive's low-power, low-latency, and highly scalable D2D interface technology allows for expanding compute performance by connecting multiple dice together using an organic substrate or a silicon interposer in a 2.5D package.

OpenFive is one of a few companies with an idea-to-silicon methodology in TSMC's latest 5 nm technology, the most advanced foundry solution available with best Power-Performance-Area (PPA). Combined with OpenFive advanced 2.5D packaging solutions and high performance, low power, and low latency HBM/D2D interface IP, designers can now create systems-on-chip (SoCs) that pack more compute power into smaller form factors for AI and HPC applications.

The SiFive E7-Series is a high performance embedded 32-bit processor. The E76 configuration of the E7-Series includes SiFive Insight Trace and Debug technology, which enables core instruction trace streaming off-chip. This feature is a requirement for debugging complex real-time software stacks, as well as software verification and certification, providing software developers with deep insights into the performance and behavior of their applications.

"As a long-standing partner of TSMC through our Open Innovation Platform (OIP) Value Chain Aggregator (VCA) program, OpenFive drives leading-edge 5 nm SoC solutions for HPC/AI, networking, and storage applications," said Sajiv Dalal, Senior Vice President of Business Management, TSMC North America. "OpenFive's custom silicon solutions with differentiated IP, combined with TSMC's N5 process, enable our mutual customers to create next generation SoCs that are highly optimized for power, performance, and cost."

"The teams at OpenFive and TSMC have worked together on numerous customer projects across multiple process generations," said Shafy Eltoukhy, CEO of OpenFive. "With the excellent support we received from TSMC, we completed this 5 nm tape out in record time, and we are looking forward to enabling chip and system companies to accelerate their designs on TSMC's leading-edge 5 nm technology."

Availability

OpenFive's 5 nm silicon solution for HPC/AI, networking and storage solutions is ready for customer design starts. First 5 nm silicon is expected to be available in Q2 2021.

View at TechPowerUp Main Site

The SoC features an OpenFive High Bandwidth Memory (HBM3) IP subsystem and D2D I/Os, as well as a SiFive E76 32-bit CPU core. The HBM3 interface supports 7.2 Gbps speeds allowing high throughput memories to feed domain-specific accelerators in compute-intensive applications including HPC, AI, Networking, and Storage. OpenFive's low-power, low-latency, and highly scalable D2D interface technology allows for expanding compute performance by connecting multiple dice together using an organic substrate or a silicon interposer in a 2.5D package.

OpenFive is one of a few companies with an idea-to-silicon methodology in TSMC's latest 5 nm technology, the most advanced foundry solution available with best Power-Performance-Area (PPA). Combined with OpenFive advanced 2.5D packaging solutions and high performance, low power, and low latency HBM/D2D interface IP, designers can now create systems-on-chip (SoCs) that pack more compute power into smaller form factors for AI and HPC applications.

The SiFive E7-Series is a high performance embedded 32-bit processor. The E76 configuration of the E7-Series includes SiFive Insight Trace and Debug technology, which enables core instruction trace streaming off-chip. This feature is a requirement for debugging complex real-time software stacks, as well as software verification and certification, providing software developers with deep insights into the performance and behavior of their applications.

"As a long-standing partner of TSMC through our Open Innovation Platform (OIP) Value Chain Aggregator (VCA) program, OpenFive drives leading-edge 5 nm SoC solutions for HPC/AI, networking, and storage applications," said Sajiv Dalal, Senior Vice President of Business Management, TSMC North America. "OpenFive's custom silicon solutions with differentiated IP, combined with TSMC's N5 process, enable our mutual customers to create next generation SoCs that are highly optimized for power, performance, and cost."

"The teams at OpenFive and TSMC have worked together on numerous customer projects across multiple process generations," said Shafy Eltoukhy, CEO of OpenFive. "With the excellent support we received from TSMC, we completed this 5 nm tape out in record time, and we are looking forward to enabling chip and system companies to accelerate their designs on TSMC's leading-edge 5 nm technology."

Availability

OpenFive's 5 nm silicon solution for HPC/AI, networking and storage solutions is ready for customer design starts. First 5 nm silicon is expected to be available in Q2 2021.

View at TechPowerUp Main Site