Raevenlord

News Editor

- Joined

- Aug 12, 2016

- Messages

- 3,755 (1.18/day)

- Location

- Portugal

| System Name | The Ryzening |

|---|---|

| Processor | AMD Ryzen 9 5900X |

| Motherboard | MSI X570 MAG TOMAHAWK |

| Cooling | Lian Li Galahad 360mm AIO |

| Memory | 32 GB G.Skill Trident Z F4-3733 (4x 8 GB) |

| Video Card(s) | Gigabyte RTX 3070 Ti |

| Storage | Boot: Transcend MTE220S 2TB, Kintson A2000 1TB, Seagate Firewolf Pro 14 TB |

| Display(s) | Acer Nitro VG270UP (1440p 144 Hz IPS) |

| Case | Lian Li O11DX Dynamic White |

| Audio Device(s) | iFi Audio Zen DAC |

| Power Supply | Seasonic Focus+ 750 W |

| Mouse | Cooler Master Masterkeys Lite L |

| Keyboard | Cooler Master Masterkeys Lite L |

| Software | Windows 10 x64 |

A recent Google study led by Mirhoseini et al. and published in Nature details how AI can be leveraged to improve upon semiconductor design practices currently employed - and which are the result of more than 60 years of engineering and physics studies. The paper describes a trained machine-learning 'agent' that can successfully place macro blocks, one by one, into a chip layout. This agent has a brain-inspired architecture known as a deep neural network, and is trained using a paradigm called reinforcement learning - where positive changes to a design are committed to memory as possible solutions, while negative changes are discarded, effectively allowing the neural network to build a decision-tree of sorts that's optimized every step of the way.

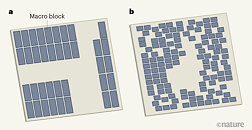

The AI isn't applied to every stage of microchip design as of yet, but that will surely change in years to come. For now, the AI is only being employed in the chip floorplanning stage of microchip production, which is actually one of the more painstaking ones. Essentially, microchip designers have to place macro blocks on their semiconductor designs - pre-made arrangements of transistors whose placement relative to one another and to the rest of the chips' components are of seminal importance for performance and efficiency targets. Remember that electric signals have to traverse different chip components to achieve a working semiconductor, and the way these are arranged in the floorplanning stage can have tremendous impact on performance characteristics of a given chip. Image A, below, showcases the tidy design a human engineer would favor - while image B showcases the apparently chaotic nature of the AI's planning.

While floorplanning carried out by human designers is a painstakingly long process that can take weeks or months between architecture iterations, the AI described in the study can achieve designs that are better compared to human specialist-designed ones in under six hours - and immense amount of time savings, with added performance and power improvements also to be considered, that could allow for much shorter development times for microchips. The AI has even shown ability to solve placement issues it never has dealt with before - the study explains that the system was trained on over 10,000 microchip designs, and that when faced with a selection of macro blocks to arrange in the floorplanning stage of microchip design, novelty iterations of components were found to outperform those designed by teams of human engineers.

View at TechPowerUp Main Site

The AI isn't applied to every stage of microchip design as of yet, but that will surely change in years to come. For now, the AI is only being employed in the chip floorplanning stage of microchip production, which is actually one of the more painstaking ones. Essentially, microchip designers have to place macro blocks on their semiconductor designs - pre-made arrangements of transistors whose placement relative to one another and to the rest of the chips' components are of seminal importance for performance and efficiency targets. Remember that electric signals have to traverse different chip components to achieve a working semiconductor, and the way these are arranged in the floorplanning stage can have tremendous impact on performance characteristics of a given chip. Image A, below, showcases the tidy design a human engineer would favor - while image B showcases the apparently chaotic nature of the AI's planning.

While floorplanning carried out by human designers is a painstakingly long process that can take weeks or months between architecture iterations, the AI described in the study can achieve designs that are better compared to human specialist-designed ones in under six hours - and immense amount of time savings, with added performance and power improvements also to be considered, that could allow for much shorter development times for microchips. The AI has even shown ability to solve placement issues it never has dealt with before - the study explains that the system was trained on over 10,000 microchip designs, and that when faced with a selection of macro blocks to arrange in the floorplanning stage of microchip design, novelty iterations of components were found to outperform those designed by teams of human engineers.

View at TechPowerUp Main Site