Raevenlord

News Editor

- Joined

- Aug 12, 2016

- Messages

- 3,755 (1.21/day)

- Location

- Portugal

| System Name | The Ryzening |

|---|---|

| Processor | AMD Ryzen 9 5900X |

| Motherboard | MSI X570 MAG TOMAHAWK |

| Cooling | Lian Li Galahad 360mm AIO |

| Memory | 32 GB G.Skill Trident Z F4-3733 (4x 8 GB) |

| Video Card(s) | Gigabyte RTX 3070 Ti |

| Storage | Boot: Transcend MTE220S 2TB, Kintson A2000 1TB, Seagate Firewolf Pro 14 TB |

| Display(s) | Acer Nitro VG270UP (1440p 144 Hz IPS) |

| Case | Lian Li O11DX Dynamic White |

| Audio Device(s) | iFi Audio Zen DAC |

| Power Supply | Seasonic Focus+ 750 W |

| Mouse | Cooler Master Masterkeys Lite L |

| Keyboard | Cooler Master Masterkeys Lite L |

| Software | Windows 10 x64 |

Western Digital has apparently delayed the introduction of Penta Layer Cell (PLC) NAND-based flash to 2025. The company had already disclosed development on the technology back in 2019, around the same time that Toshiba announced it (Toshiba which is now Kioxia, and a Western Digital partner in the development of the technology). The information was disclosed at Bank of America Merrill Lynch 2021 Global Technology Conference, where Western Digital's technology and strategy chief Siva Sivaram said that "I expect that transition [from QLC to PLC] will be slower. So maybe in the second half of this decade we are going to see some segments starting to get 5 bits per cell."

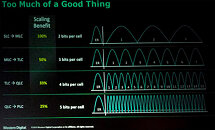

PLC is another density-increase step for NAND flash, whereby each NAND cell can have five bits written into it, thus increasing the amount of information available in the same NAND footprint. To achieve these 5 bits, each cell must store one of 32 voltage states, which in turn inform the flash controller of which corresponding data bits are stored herein. Siva Sivaram said that he expect the technology to take some more time to mature than most, due to the need for controller development that can take advantage of the increased density while making up for the shortcoming in this increased bit-per-cell approach (lower endurance and lower performance). PLC won't bring us HDD-tier storage density by itself (it only enables storage of 25% more data per cell); however, when paired with increasing layers of NAND flash, those 25% extra quickly add up.

View at TechPowerUp Main Site

PLC is another density-increase step for NAND flash, whereby each NAND cell can have five bits written into it, thus increasing the amount of information available in the same NAND footprint. To achieve these 5 bits, each cell must store one of 32 voltage states, which in turn inform the flash controller of which corresponding data bits are stored herein. Siva Sivaram said that he expect the technology to take some more time to mature than most, due to the need for controller development that can take advantage of the increased density while making up for the shortcoming in this increased bit-per-cell approach (lower endurance and lower performance). PLC won't bring us HDD-tier storage density by itself (it only enables storage of 25% more data per cell); however, when paired with increasing layers of NAND flash, those 25% extra quickly add up.

View at TechPowerUp Main Site