- Joined

- Aug 19, 2017

- Messages

- 2,651 (0.99/day)

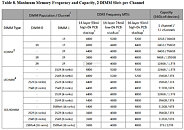

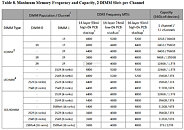

Just yesterday, thanks to the Linux driver update, we found information stating that AMD's upcoming EPYC Genoa processor generation based on Zen 4 core IP will have a 12-channel memory controller. However, we didn't know how AMD engineered the memory controller of this processor generation and some of its maximum capabilities. However, there is an exciting discovery. According to the report from ComputerBase, with information exclusive to them, AMD will enable up to 12 TB of DDR5 memory spread across 12 memory channels. The processor supports DDR5-5200 memory, but when all 24 memory slots (two per channel) are populated, the DDR5 maximum speed drops to 4000 MT/s.

It is unclear why this is the case, and if any difficulties were designing the controller, so the maximum speed drops when every slot is used. One reassuring thing is that the bandwidth created by 12 memory channels should be sufficient to make up for the lost speed of DDR5 memory reduction.

View at TechPowerUp Main Site

It is unclear why this is the case, and if any difficulties were designing the controller, so the maximum speed drops when every slot is used. One reassuring thing is that the bandwidth created by 12 memory channels should be sufficient to make up for the lost speed of DDR5 memory reduction.

View at TechPowerUp Main Site