- Joined

- Oct 9, 2007

- Messages

- 47,635 (7.44/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | Gigabyte B550 AORUS Elite V2 |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 16GB DDR4-3200 |

| Video Card(s) | Galax RTX 4070 Ti EX |

| Storage | Samsung 990 1TB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

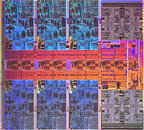

Intel's next-generation "Meteor Lake-P" mobile processor with a 6P+8E Compute Tile was shown off at the 2022 IEEE VLSI Symposium on Tech and Circuits (6 performance cores and 8 efficiency cores). We now have annotations for all four tiles, as well as a close-up die-shot of the Compute Tile. Intel also confirmed that the Compute Tile will be built on its homebrew Intel 4 silicon fabrication process, which offers over 20% iso-power performance increase versus the Intel 7 node, through extensive use of EUV lithography.

We had earlier seen a 2P+8E version of the "Meteor Lake" Compute Tile, probably from the "Meteor Lake-U" package. The larger 6P+8E Compute tile features six "Redwood Cove" performance cores, and two "Crestmont" efficiency core clusters, each with four E-cores. Assuming the L3 cache slice per P-core or E-core cluster is 2.5 MB, there has to be 20 MB of L3 cache on the compute tile. Each P-core has 2 MB of dedicated L2 cache, while each of the two E-core clusters shares 4 MB of L2 cache among four E-cores.

Elsewhere in the SoC, we see the three other tiles—the iGPU Tile (dubbed GFX Tile), the SoC Tile, and the I/O tile. The GFX Tile packs the iGPU, which is possibly a more power-dense component than even a P-core, and so this tile very likely gets the most advanced silicon fabrication node on the package, which is very likely the TSMC N3 (3 nm). The SoC Tile packs uncore and high-bandwidth I/O components, including the memory controllers, PCI-Express 5.0 root complex, Management Engine, etc.

The I/O Tile is essentially an integrated PCH that handles platform I/O that isn't as bandwidth heavy has the main PEG interface, or the main Gen 5 NVMe interface. This tile could be built on the least advanced fabrication process. All four tiles are placed on a silicon interposer through 3D Foveros technology. The interposer is a silicon die that facilitates high-density microscopic wiring between dies in a multi-chip module; and appears like a single contiguous die to the fiberglass substrate.

View at TechPowerUp Main Site

We had earlier seen a 2P+8E version of the "Meteor Lake" Compute Tile, probably from the "Meteor Lake-U" package. The larger 6P+8E Compute tile features six "Redwood Cove" performance cores, and two "Crestmont" efficiency core clusters, each with four E-cores. Assuming the L3 cache slice per P-core or E-core cluster is 2.5 MB, there has to be 20 MB of L3 cache on the compute tile. Each P-core has 2 MB of dedicated L2 cache, while each of the two E-core clusters shares 4 MB of L2 cache among four E-cores.

Elsewhere in the SoC, we see the three other tiles—the iGPU Tile (dubbed GFX Tile), the SoC Tile, and the I/O tile. The GFX Tile packs the iGPU, which is possibly a more power-dense component than even a P-core, and so this tile very likely gets the most advanced silicon fabrication node on the package, which is very likely the TSMC N3 (3 nm). The SoC Tile packs uncore and high-bandwidth I/O components, including the memory controllers, PCI-Express 5.0 root complex, Management Engine, etc.

The I/O Tile is essentially an integrated PCH that handles platform I/O that isn't as bandwidth heavy has the main PEG interface, or the main Gen 5 NVMe interface. This tile could be built on the least advanced fabrication process. All four tiles are placed on a silicon interposer through 3D Foveros technology. The interposer is a silicon die that facilitates high-density microscopic wiring between dies in a multi-chip module; and appears like a single contiguous die to the fiberglass substrate.

View at TechPowerUp Main Site