- Joined

- Aug 19, 2017

- Messages

- 2,847 (1.03/day)

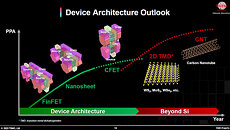

During the European Technology Symposium 2023, TSMC presented additional details regarding the upcoming complementary FET (CFET) technology to power the next generation of silicon-based devices. With Nanosheet replacing FinFET, the CFET technology will do the same to the Gate All Around FET (GAAFET) Nanosheet nodes. As the company notes, CFET transistors are now in the TSMC labs and are being tested for performance, efficiency, and density. Compared to GAAFET, CFET will provide greater design in all of those areas, but it will require some additional manufacturing steps to get the chip working as intended. Integrating both p-type and n-type FETs into a single device, CFET will require the use of High NA EUV scanners with high precision and high power to manufacture it.

The use of CFET, as the roadmap shows, is one of the last steps in the world of silicon. It will require the integration of new materials into the manufacturing process, resulting in a greater investment into research and development that is in charge of node creation. Kevin Zhang, senior vice president at TSMC, responsible for technology roadmap and business development, notes: "Let me make a clarification on that roadmap, everything beyond the Nanosheet is something we will put on our [roadmap] to tell you there is still future out there. We will continue to work on different options. I also have the add on to the one-dimensional material-[based transistors] […], all of those are being researched on being investigated on the future potential candidates right now, we will not tell you exactly the transistor architecture will be beyond the Nanosheet."

Even though the company is working on CFETs, a new technology may emerge as research continues. The only thing "set in stone" is the nanosheet GAAGET technology that will start at 2 nm node. Additionally, Zhang added: "So this Nanosheet is starting at 2nm, it is reasonable to project and that Nanosheet will be used for at least a couple of generations, right? So, if you think about CFETs, we've leveraged [FinFETs] for five generations, which is more than 10 years. Maybe [device structure] is somebody else's problem to worry, then you can continue to write a story."

View at TechPowerUp Main Site | Source

The use of CFET, as the roadmap shows, is one of the last steps in the world of silicon. It will require the integration of new materials into the manufacturing process, resulting in a greater investment into research and development that is in charge of node creation. Kevin Zhang, senior vice president at TSMC, responsible for technology roadmap and business development, notes: "Let me make a clarification on that roadmap, everything beyond the Nanosheet is something we will put on our [roadmap] to tell you there is still future out there. We will continue to work on different options. I also have the add on to the one-dimensional material-[based transistors] […], all of those are being researched on being investigated on the future potential candidates right now, we will not tell you exactly the transistor architecture will be beyond the Nanosheet."

Even though the company is working on CFETs, a new technology may emerge as research continues. The only thing "set in stone" is the nanosheet GAAGET technology that will start at 2 nm node. Additionally, Zhang added: "So this Nanosheet is starting at 2nm, it is reasonable to project and that Nanosheet will be used for at least a couple of generations, right? So, if you think about CFETs, we've leveraged [FinFETs] for five generations, which is more than 10 years. Maybe [device structure] is somebody else's problem to worry, then you can continue to write a story."

View at TechPowerUp Main Site | Source