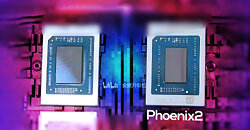

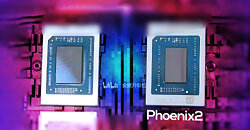

Talking with XDA-Developers, AMD has confirmed more details about the upcoming Phoenix2 APU, which should debut with Ryzen 3 7440U and Ryzen 5 7540U APUs. Unlike the larger Phoenix APU, the Phoenix2 APU will have a hybrid design with Zen 4 and Zen 4c cores. As confirmed by AMD, the Phoenix2 APU will be a 6-core design, which makes it pretty clear it will feature two Zen 4 and four Zen 4c cores. It will also come with a Radeon 740M GPU with 4 RDNA3 compute units (CUs). The Phoenix2 APU will also lack the Ryzen AI core. Unlike Intel's hybrid approach, Zen 4c cores will have the same IPC as Zen 4, same instructions, but have less L3 cache per core.

AMD has previously confirmed that the Ryzen 3 7440U will have a smaller die size of 137 mm², compared to 178 mm² on the Ryzen 5 7640U. While AMD did not directly confirmed that the Ryzen 5 7540U will also be based on the Phoenix2 APU, official specification shows it with the same 4 GPU cores and without Ryzen AI core, making it pretty obvious it will be based on the same Phoenix2 APU. Hopefully, AMD will come up with more official details about its Phoenix2 APU as there are still a lot of unknowns.

View at TechPowerUp Main Site | Source

AMD has previously confirmed that the Ryzen 3 7440U will have a smaller die size of 137 mm², compared to 178 mm² on the Ryzen 5 7640U. While AMD did not directly confirmed that the Ryzen 5 7540U will also be based on the Phoenix2 APU, official specification shows it with the same 4 GPU cores and without Ryzen AI core, making it pretty obvious it will be based on the same Phoenix2 APU. Hopefully, AMD will come up with more official details about its Phoenix2 APU as there are still a lot of unknowns.

View at TechPowerUp Main Site | Source