- Joined

- Aug 19, 2017

- Messages

- 3,205 (1.11/day)

During the 69th annual IEEE International Electron Devices Meeting (IEDM), Intel demonstrated some of its latest transistor design and manufacturing advancements. The first one in line is the 3D integration of transistors. According to Intel, the company has successfully stacked complementary field effect transistors (CFET) at a scaled gate pitch down to 60 nm. With CFETs promising thinner gate channels, the 3D stacked CFET would allow for higher density by going vertically and horizontally. Intel's 7 node has a 54 nm gate pitch, meaning CFETs are already close to matching production-ready nodes. With more time and development, we expect to see 3D stacked CFETs in the production runs in the coming years.

Next, Intel has demonstrated RibbonFET technology, a novel approach that is the first new transistor architecture since the introduction of FinFET in 2012. Using ribbon-shaped channels surrounded by the gate, these transistors allow for better control and higher drive current at all voltage levels. This allows faster transistor switching speeds, which later lead to higher frequency and performance. The width of these nanoribbon channels can be modulated depending on the application, where low-power mobile applications use less current, making the channels thinner, and high-performance applications require more current, making the channels wider. One stack of nanoribbons can achieve the same drive current as multiple fins found in FinFET but at a smaller footprint.

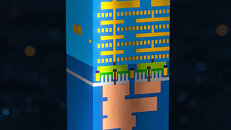

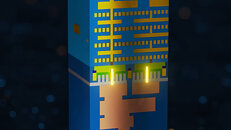

Next up, we learn that Intel has commented that its PowerVia technology is production-ready, with the first products utilizing PowerVia expected to arrive in 2024. PowerVia is Intel's efforts to change the structure of the transistor power delivery, moving the power routing wires from the top to below the transistor in an effort to manage power efficiently and not obscure signal wires found on the top of the transistor. PowerVia is formed into a backside power delivery network that operates without contact with the single network in the chip. The connection to the transistor layer is made using nano through silicon vias (TSVs), which are 500 times smaller than regular TSVs.

Intel has also demonstrated the integration of silicon and GaN. The company successfully established a high-performance, large-scale integrated circuit solution called "DrGaN" for power delivery. This solution can potentially enable power delivery solutions to keep pace with the power density and efficiency demands of future computing. Additionally, the company will also present transition metal dichalcogenide (TMD) 2D channel materials, which offer a scaling path for transistor physical gate length below 10 nm. Intel is scheduled to demonstrate prototypes of the CMOS design's high-mobility TMD transistors for NMOS (n-channel metal oxide semiconductor) and PMOS (p-channel metal oxide semiconductor) elements. Lastly, the company will also present the so-claimed world's first gate-all-around (GAA) 2D TMD PMOS transistor and the world's first 2D PMOS transistor fabricated on a 300 mm wafer, all dedicated to scaling transistor density further.

View at TechPowerUp Main Site | Source

Next, Intel has demonstrated RibbonFET technology, a novel approach that is the first new transistor architecture since the introduction of FinFET in 2012. Using ribbon-shaped channels surrounded by the gate, these transistors allow for better control and higher drive current at all voltage levels. This allows faster transistor switching speeds, which later lead to higher frequency and performance. The width of these nanoribbon channels can be modulated depending on the application, where low-power mobile applications use less current, making the channels thinner, and high-performance applications require more current, making the channels wider. One stack of nanoribbons can achieve the same drive current as multiple fins found in FinFET but at a smaller footprint.

Next up, we learn that Intel has commented that its PowerVia technology is production-ready, with the first products utilizing PowerVia expected to arrive in 2024. PowerVia is Intel's efforts to change the structure of the transistor power delivery, moving the power routing wires from the top to below the transistor in an effort to manage power efficiently and not obscure signal wires found on the top of the transistor. PowerVia is formed into a backside power delivery network that operates without contact with the single network in the chip. The connection to the transistor layer is made using nano through silicon vias (TSVs), which are 500 times smaller than regular TSVs.

Intel has also demonstrated the integration of silicon and GaN. The company successfully established a high-performance, large-scale integrated circuit solution called "DrGaN" for power delivery. This solution can potentially enable power delivery solutions to keep pace with the power density and efficiency demands of future computing. Additionally, the company will also present transition metal dichalcogenide (TMD) 2D channel materials, which offer a scaling path for transistor physical gate length below 10 nm. Intel is scheduled to demonstrate prototypes of the CMOS design's high-mobility TMD transistors for NMOS (n-channel metal oxide semiconductor) and PMOS (p-channel metal oxide semiconductor) elements. Lastly, the company will also present the so-claimed world's first gate-all-around (GAA) 2D TMD PMOS transistor and the world's first 2D PMOS transistor fabricated on a 300 mm wafer, all dedicated to scaling transistor density further.

View at TechPowerUp Main Site | Source

....

....