- Joined

- Oct 9, 2007

- Messages

- 47,424 (7.51/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

JEDEC Solid State Technology Association, the global leader in standards development for the microelectronics industry, today announced publication of the JESD79-5C DDR5 SDRAM standard. This important update to the JEDEC DDR5 SDRAM standard includes features designed to improve reliability and security and enhance performance in a wide range of applications from high-performance servers to emerging technologies such as AI and machine learning. JESD79-5C is now available for download from the JEDEC website.

JESD79-5C introduces an innovative solution to improve DRAM data integrity called Per-Row Activation Counting (PRAC). PRAC precisely counts DRAM activations on a wordline granularity. When PRAC-enabled DRAM detects an excessive number of activations, it alerts the system to pause traffic and to designate time for mitigative measures. These interrelated actions underpin PRAC's ability to provide a fundamentally accurate and predictable approach for addressing data integrity challenges through close coordination between the DRAM and the system.

Additional features offered in JESD79-5C DDR5 include:

"The JC-42 Committee is pleased to unveil PRAC, a comprehensive solution to help ensure DRAM data integrity, as an integral component of the DDR5 update. Work is underway to incorporate this feature into other DRAM product families within JEDEC," noted Christopher Cox, JC-42 Committee Chair.

View at TechPowerUp Main Site

JESD79-5C introduces an innovative solution to improve DRAM data integrity called Per-Row Activation Counting (PRAC). PRAC precisely counts DRAM activations on a wordline granularity. When PRAC-enabled DRAM detects an excessive number of activations, it alerts the system to pause traffic and to designate time for mitigative measures. These interrelated actions underpin PRAC's ability to provide a fundamentally accurate and predictable approach for addressing data integrity challenges through close coordination between the DRAM and the system.

Additional features offered in JESD79-5C DDR5 include:

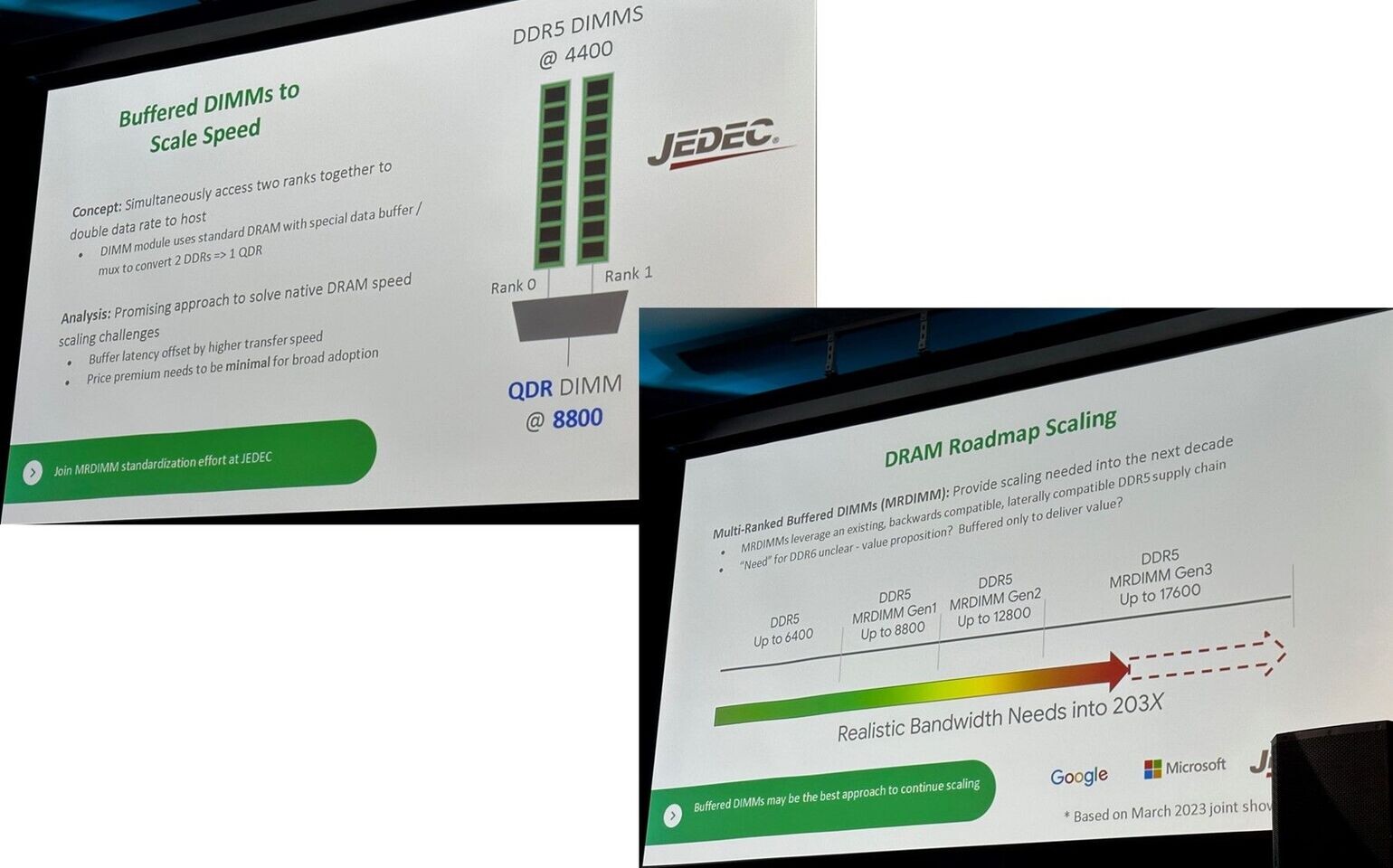

- Expansion of timing parameters definition from 6800 Mbps to 8800 Mbps

- Inclusion of DRAM core timings and Tx/Rx AC timings extended up to 8800 Mbps, compared to the previous version which supported only up to 6400 timing parameters and partial pieces up to 7200 DRAM core timings

- Introduction of Self-Refresh Exit Clock Sync for I/O Training Optimization

- Incorporation of DDP (Dual-Die Package) timings

- Deprecation of PASR (Partial Array Self Refresh) to address security concerns

"The JC-42 Committee is pleased to unveil PRAC, a comprehensive solution to help ensure DRAM data integrity, as an integral component of the DDR5 update. Work is underway to incorporate this feature into other DRAM product families within JEDEC," noted Christopher Cox, JC-42 Committee Chair.

View at TechPowerUp Main Site