- Joined

- Oct 9, 2007

- Messages

- 47,193 (7.56/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

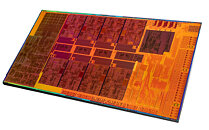

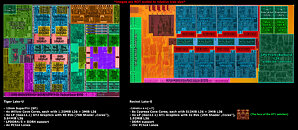

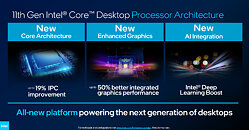

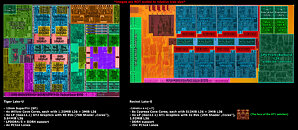

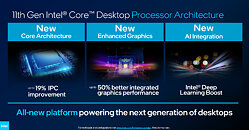

Intel is betting big on an 8-core processor to revive its gaming performance leadership, and that chip is the 11th Generation Core "Rocket Lake-S," coming this March. In its 2021 International CES online event, Intel disclosed more details about "Rocket Lake-S," including the first true-color die-shot. PC enthusiast @Locuza_ on Twitter annotated the die for your viewing pressure. For starters, nearly half the die-area of the "Rocket Lake-S" is taken up by the uncore and iGPU, with the rest going to the eight "Cypress Cove" CPU cores.

The "Cypress Cove" CPU core is reportedly a back-port of "Willow Cove" to the 14 nm silicon fabrication node, although there are some changes, beginning with its cache hierarchy. A "Cypress Cove" core is configured with the same L1I and L1D cache sizes as "Willow Cove," but differ with L2 and L3 cache sizes. Each "Cypress Cove" core is endowed with 512 KB of dedicated L2 cache (which is a 100% increase from the 256 KB on "Skylake" cores); but this pales in comparison to the 1.25 MB L2 caches of "Willow Cove" cores on the "Tiger Lake-U" silicon. Also, the L3 cache for the 8-core "Rocket Lake-S" die is 16 MB, spread across eight 2 MB slices; while the 4-core "Tiger Lake-U" features 12 MB of L3, spread across four 3 MB slices. Each core can address the whole L3 cache, across all slices.

The next big component on "Rocket Lake-S" is the Gen12 Xe-LP GT1 integrated graphics. The "GT1" differentiator denotes the smallest trim of Xe-LP, and amounts to 32 EU (execution units). The "Tiger Lake-U" silicon features the larger "GT2" trim of Gen12 Xe-LP, with 96 EU. Intel could give the GT1 on "Rocket Lake-S" some lavish clock boosting headroom on virtue of this being a desktop processor, to try and overcome some of the EU shortfall compared to "Tiger Lake-U." Even with just 32 EU, Intel is claiming a 50% iGPU performance gain compared to the Gen9.5 GT2 iGPU on "Comet Lake-S."

The third major component is the uncore, which looks visibly larger than the one on the 8-core "Coffee Lake Refresh" silicon. This is because it features a PCI-Express Gen 4.0 switching fabric, and additional SerDes to put out 28 PCIe lanes, compared to just 20 on the older generation. We imagine the memory controllers are largely unchanged, as Intel is sticking with dual-channel DDR4 as the memory standard for "Rocket Lake-S." The switch to DDR5 could probably herald a new socket, with "Alder Lake-S."

View at TechPowerUp Main Site

The "Cypress Cove" CPU core is reportedly a back-port of "Willow Cove" to the 14 nm silicon fabrication node, although there are some changes, beginning with its cache hierarchy. A "Cypress Cove" core is configured with the same L1I and L1D cache sizes as "Willow Cove," but differ with L2 and L3 cache sizes. Each "Cypress Cove" core is endowed with 512 KB of dedicated L2 cache (which is a 100% increase from the 256 KB on "Skylake" cores); but this pales in comparison to the 1.25 MB L2 caches of "Willow Cove" cores on the "Tiger Lake-U" silicon. Also, the L3 cache for the 8-core "Rocket Lake-S" die is 16 MB, spread across eight 2 MB slices; while the 4-core "Tiger Lake-U" features 12 MB of L3, spread across four 3 MB slices. Each core can address the whole L3 cache, across all slices.

The next big component on "Rocket Lake-S" is the Gen12 Xe-LP GT1 integrated graphics. The "GT1" differentiator denotes the smallest trim of Xe-LP, and amounts to 32 EU (execution units). The "Tiger Lake-U" silicon features the larger "GT2" trim of Gen12 Xe-LP, with 96 EU. Intel could give the GT1 on "Rocket Lake-S" some lavish clock boosting headroom on virtue of this being a desktop processor, to try and overcome some of the EU shortfall compared to "Tiger Lake-U." Even with just 32 EU, Intel is claiming a 50% iGPU performance gain compared to the Gen9.5 GT2 iGPU on "Comet Lake-S."

The third major component is the uncore, which looks visibly larger than the one on the 8-core "Coffee Lake Refresh" silicon. This is because it features a PCI-Express Gen 4.0 switching fabric, and additional SerDes to put out 28 PCIe lanes, compared to just 20 on the older generation. We imagine the memory controllers are largely unchanged, as Intel is sticking with dual-channel DDR4 as the memory standard for "Rocket Lake-S." The switch to DDR5 could probably herald a new socket, with "Alder Lake-S."

View at TechPowerUp Main Site