Monday, January 11th 2021

Dual-CCD Ryzen 5 5600X and Ryzen 7 5800X In the Wild

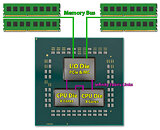

Certain AMD Ryzen 5 5600X and Ryzen 7 5800X processors are physically based on a dual-CCD design, according to an investigative report by Igor's Lab and Yuri "1usmus" Bubliy. The 5600X and 5800X are normally meant to be single-CCD processors owing to their core-counts. Based on the "Vermeer" multi-chip module design, the Ryzen 5000 series desktop processors use up to two 8-core CCDs to achieve their core-counts of up to 16 cores, with the 6-core 5600X and 8-core 5800X normally having just one CCD; while the 12-core 5900X and 16-core 5950X use two.

There are, apparently, some 5600X and 5800X built from dual-CCD MCMs, in which an entire CCD, although physically present on the package, is disabled. A 5600X based on a dual-CCD design is essentially a 5900X from which one of the CCDs didn't fully qualify; while the 5800X dual-CCD is a 5950X in which one such die didn't quite make the cut. There's no telling which CCD is disabled, it could be CCD 0 or CCD 1, those with CCD 0 disabled could trigger minor (benign) UI bugs with certain tuning utilities, which is how Wallossek and Bubliy discovered these chips. In any case, you're getting a 5600X or 5800X that works as advertised, and is fully covered by AMD's product warranties. Igor's Lab is investigating further into these dual-CCD 5600X and 5800X chips, and is probing the possibility of unlocking them to Ryzen 9.

Source:

Igor's Lab

There are, apparently, some 5600X and 5800X built from dual-CCD MCMs, in which an entire CCD, although physically present on the package, is disabled. A 5600X based on a dual-CCD design is essentially a 5900X from which one of the CCDs didn't fully qualify; while the 5800X dual-CCD is a 5950X in which one such die didn't quite make the cut. There's no telling which CCD is disabled, it could be CCD 0 or CCD 1, those with CCD 0 disabled could trigger minor (benign) UI bugs with certain tuning utilities, which is how Wallossek and Bubliy discovered these chips. In any case, you're getting a 5600X or 5800X that works as advertised, and is fully covered by AMD's product warranties. Igor's Lab is investigating further into these dual-CCD 5600X and 5800X chips, and is probing the possibility of unlocking them to Ryzen 9.

62 Comments on Dual-CCD Ryzen 5 5600X and Ryzen 7 5800X In the Wild

Ew no, the single biggest reason Zen3 is so good is because of the unified cache and lower latency that brings.Splitting 6 or 8 cores over two CCDs is basically assembling a Zen2 CPU out of reject Zen3 parts, and everyone already has a Zen2.

Okay, I calmed down enough to read the second paragraph now.

I wonder why they're doing this? Can it really be cheaper to produce all CPUs the same dual-CCD way and just disable chips where one of them has too much damage to even make a 6-core?

But they will also make 5900x's that do not work properly so they can just sell that as a 5600x when disabling one of the two CCD.

This way they can still sell that chip instead of just having to throw it all away.

I was wondering if yields (and profits on higher-end parts) were such that it actually made economic sense for AMD to just produce dual-die parts and only the failed ones make a 5600X.

When I spend more than five seconds thinking about it though, that's unlikely because then you'd have a fair few chips that were 8C+6C, wasting a very valuable 8C die.

Do you think it's because AMD bin the 6-core dies before packaging two of them on the same CPU, and then discover that they didn't both survive the packaging process?

It's not like this will make any difference whatsoever when it comes to performance, so ... more of a curiosity than anything else. Good on AMD for not being wasteful, I guess?

At the end of the day, this is all speculation until 1usmus takes one of the aforementioned sus CPUs that has difficulties with CTR, and delids (ie. destroys) it to verify if it really has 2 CCDs.

And no, this isn't Renoir; having extra dead silicon doesn't help thermal dissipation at all when the chiplets aren't even physically connected.

Makes me think of the 10-core rumors, and what AMD could do if they could tweak the design to accept asymmetric CCDs. I remember reading that the 5900X and 5950X are very heavily skewed towards the better CCD in terms of clocks, power draw and load. Maybe if that second CCD is less important, it doesn't need to be binned to such high standards.

It's also likely that the chips' frequency limit, power etc. can't be determined very accurately before they're put on substrate, and electrical characteristics are affected by the substrate and socket and PCB anyway, so again, a small number doesn't make it through testing. Or they would have to be sold as 5900T, hah.

Edit: it's also possible that some I/O dies aren't fully functional or can't clock high enough, which is discovered too late in the manufacturing process.

AMD have to bin the best chips for the 5950X, but if one of the chiplets doesn't even work, why would they put said chiplet in a 5950X in the first place?

Or is it a way to quickly adapt to market demand? Neuter one chiplet and call it a day?

However, if he or someone else successfully revives the inactive CCD and puts the processor through some tests, the results would reveal a lot about why AMD is doing this.

I agree with other speculation that these were former ryzen 9 parts that failed validation after manufacture being repurposed as lower end products.

It's not splitting core allocation across CCD.

Remember my 3 core Athlon that unlocked to 4 core Phenom II that I paid like $50 for it.

Those were good ole days.