Intel "Meteor Lake" a "Breakthrough Client Processor" Leveraging Foveros Packaging

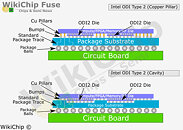

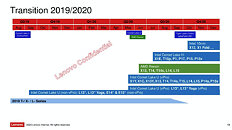

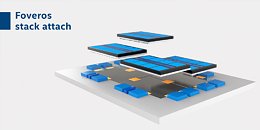

Intel CEO Pat Gelsinger made the first official reference to the company's future-generation client processor, codenamed "Meteor Lake." Slated for market release in 2023, the processor's compute tile will be taped out in Q2-2021. Launching alongside the "Granite Rapids" enterprise processor, "Meteor Lake" will be a multi-chip module leveraging Intel's Foveros chip packaging technology.

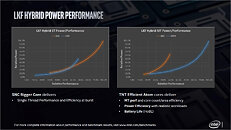

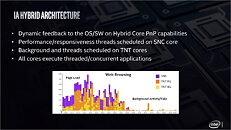

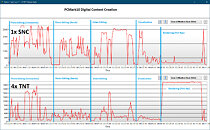

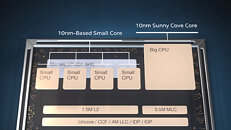

Different components of the processor will be fabricated on different kinds of silicon fabrication nodes, and interconnected on the package using EMIB inter-die connections, or even silicon interposers. The compute tile is likely the tile containing the processor's CPU cores, and Intel confirmed a 7 nm-class foundry node for it. "Meteor Lake" will be a hybrid processor, much like the upcoming "Alder Lake," meaning that it will have two kinds of CPU cores, larger "high performance" cores that remain dormant when the machine is idling or dealing with lightweight workloads; and smaller "high efficiency" cores based on a low-power microarchitecture.

Different components of the processor will be fabricated on different kinds of silicon fabrication nodes, and interconnected on the package using EMIB inter-die connections, or even silicon interposers. The compute tile is likely the tile containing the processor's CPU cores, and Intel confirmed a 7 nm-class foundry node for it. "Meteor Lake" will be a hybrid processor, much like the upcoming "Alder Lake," meaning that it will have two kinds of CPU cores, larger "high performance" cores that remain dormant when the machine is idling or dealing with lightweight workloads; and smaller "high efficiency" cores based on a low-power microarchitecture.