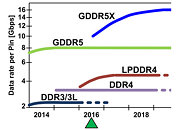

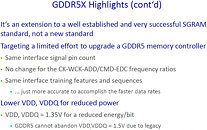

Mid-range "Pascal" GPUs Stick to GDDR5-class Memory

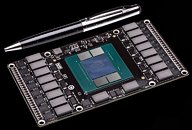

At the NVIDIA Drive PX compute module unveiling, company CEO Jen-Hsun Huang gave us the first glimpse of a mid-range GPU based on the "Pascal" architecture. This chip looks a lot more conventional than the fancy HBM2-infused multi-chip module that's at the heart of the Tesla P100. Its package is a traditional green fiberglass substrate with a rectangular die at the center; and is surrounded by conventional-looking GDDR5-class memory chips (which could very well be GDDR5X). The Drive PX is a GPU-accelerated deep-learning box that NVIDIA is basing much of its self-driving car tech around; and uses a pair of these mid-range "Pascal" MXM boards.