AMD Updates Wafer Supply Agreement with GlobalFoundries to Free Itself of "7nm Tax"

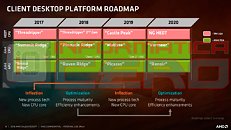

AMD in its Q4-2018 Earnings Report disclosed that it has amended its Wafer Supply Agreement (WSA) with GlobalFoundries that frees it from paying a "7 nanometer tax." Under the older version of WSA, AMD would have had to pay a penalty to GlobalFoundries if it sourced processors from any other semiconductor foundry. The company got preferential pricing in return for the exclusivity. With GlobalFoundries discontinuing development of cutting-edge processes such as 7 nm and 5 nm, it makes sense for AMD to seek out other foundry partners, such as TSMC, and an amendment to the WSA was needed. With this amendment in place, AMD can go ahead and source 7 nm dies from TSMC without paying penalties to GlobalFoundries (GloFo).

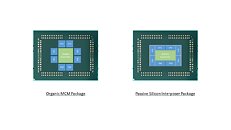

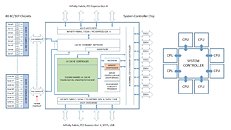

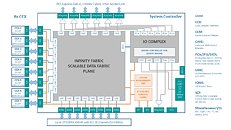

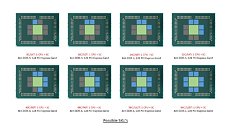

With its "Zen 2" microarchitecture, AMD is going big on multi-chip modules, in which only those components that can tangibly benefit from the switch to the 7 nm node, namely the CPU cores, would be built on 7 nm dies, called "CPU chiplets," while components that don't need the miniaturization just yet, such as the processor's memory controller, PCIe root-complex, etc., will be built on separate dies called "I/O controllers." These dies will continue to be 14 nm, and likely supplied by GloFo. Final packaging of 7 nm CPU chiplets from TSMC, and 14 nm I/O controllers from GloFo, will happen at GloFo's facilities in China or Malaysia. AMD in its amendment committed to purchasing 14 nm and 12 nm chips from GloFo between 2019 and 2021, which means the MCM approach to processors is here to stay.

With its "Zen 2" microarchitecture, AMD is going big on multi-chip modules, in which only those components that can tangibly benefit from the switch to the 7 nm node, namely the CPU cores, would be built on 7 nm dies, called "CPU chiplets," while components that don't need the miniaturization just yet, such as the processor's memory controller, PCIe root-complex, etc., will be built on separate dies called "I/O controllers." These dies will continue to be 14 nm, and likely supplied by GloFo. Final packaging of 7 nm CPU chiplets from TSMC, and 14 nm I/O controllers from GloFo, will happen at GloFo's facilities in China or Malaysia. AMD in its amendment committed to purchasing 14 nm and 12 nm chips from GloFo between 2019 and 2021, which means the MCM approach to processors is here to stay.