- Joined

- Oct 9, 2007

- Messages

- 47,233 (7.55/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

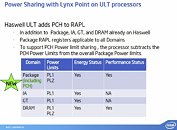

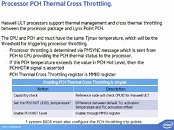

Going into 2013, Intel's tough balancing act between keeping a low power/thermal envelope, and advancing performance, all while staying on the 22 nm silicon fab process, will be care of its Core "Haswell-ULT" processor. The chip will feature some radical changes to traditional Intel processor design, which will help it achieve its design goals. According to a deck of leaked slides scored by Expreview, Intel plans to use additional C-states that drop the processor's base clock, and redesign the processor package to accommodate the PCH silicon, reducing the board footprint.

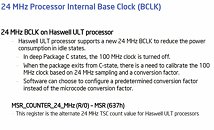

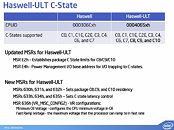

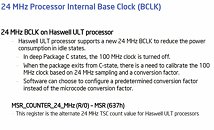

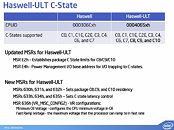

To begin with, Haswell-ULT will be designed to support 24 MHz base clock speed, which running in "deep" energy-saving idle states. Modern processors with FSB replacement interconnect technologies such as QuickPath Interconnect and HyperTransport need a base clock to time other components on the processor, and for low-level communications, while a bulk of the data is transported by the primary interconnect. Intel found a way to turn off the 100 MHz base clock signal (which is also used to time the PCI-Express root complex and integrated graphics core), and replace it with a 24 MHz clock, when the processor is idling. As the processor returns to lower (more active) C-states, the 100 MHz base clock is reapplied. The 24 MHz base clock is activated by three new power states, C8, C9, and C10, introduced by Haswell-ULT. The third slide below details what happens to the various components in the new C-states.

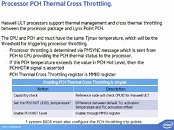

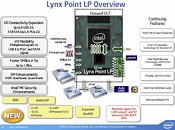

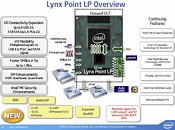

Another major change, which is a step towards building a true high-performance SoC, is the Haswell-ULT package. The package is a multi-chip module (MCM) of the processor die and the PCH (platform-controller hub, or the chipset). One shouldn't confuse this with Core "Clarkdale" processors, which were MCMs of a dual-core CPU silicon, and a GMCH (graphics memory controller hub). The CPU silicon of Haswell-ULT includes up to four x86 cores, three levels of cache, integrated memory controller, integrated graphics, and a PCI-Express root complex. The PCH silicon includes all platform interfaces, including SATA, USB, SMBus, gigabit Ethernet, and HD audio. Think of PCH as being a glorified southbridge.

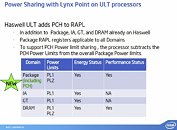

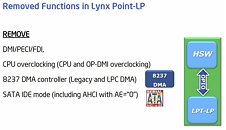

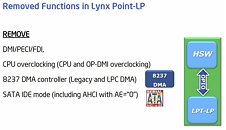

The pin-side of the Haswell-ULT package, we imagine, features only I/O and power pins, with no chipset bus. The processor and PCH dies on the package are connected by what Intel is referring to as "OPI x8," which appears to feature double the bandwidth as DMI 2.0, that's 8 GB/s. The PCH that will drive Intel's Core "Haswell" processors across the board is codenamed "Lynx Point," which will exist as dedicated PCH packages on desktop and mainstream mobile platforms, and part of the Haswell-ULT MCMs, as Lynx Point-LP, with a slightly slimmer feature-set.

View at TechPowerUp Main Site

To begin with, Haswell-ULT will be designed to support 24 MHz base clock speed, which running in "deep" energy-saving idle states. Modern processors with FSB replacement interconnect technologies such as QuickPath Interconnect and HyperTransport need a base clock to time other components on the processor, and for low-level communications, while a bulk of the data is transported by the primary interconnect. Intel found a way to turn off the 100 MHz base clock signal (which is also used to time the PCI-Express root complex and integrated graphics core), and replace it with a 24 MHz clock, when the processor is idling. As the processor returns to lower (more active) C-states, the 100 MHz base clock is reapplied. The 24 MHz base clock is activated by three new power states, C8, C9, and C10, introduced by Haswell-ULT. The third slide below details what happens to the various components in the new C-states.

Another major change, which is a step towards building a true high-performance SoC, is the Haswell-ULT package. The package is a multi-chip module (MCM) of the processor die and the PCH (platform-controller hub, or the chipset). One shouldn't confuse this with Core "Clarkdale" processors, which were MCMs of a dual-core CPU silicon, and a GMCH (graphics memory controller hub). The CPU silicon of Haswell-ULT includes up to four x86 cores, three levels of cache, integrated memory controller, integrated graphics, and a PCI-Express root complex. The PCH silicon includes all platform interfaces, including SATA, USB, SMBus, gigabit Ethernet, and HD audio. Think of PCH as being a glorified southbridge.

The pin-side of the Haswell-ULT package, we imagine, features only I/O and power pins, with no chipset bus. The processor and PCH dies on the package are connected by what Intel is referring to as "OPI x8," which appears to feature double the bandwidth as DMI 2.0, that's 8 GB/s. The PCH that will drive Intel's Core "Haswell" processors across the board is codenamed "Lynx Point," which will exist as dedicated PCH packages on desktop and mainstream mobile platforms, and part of the Haswell-ULT MCMs, as Lynx Point-LP, with a slightly slimmer feature-set.

View at TechPowerUp Main Site

Last edited: