TheLostSwede

News Editor

- Joined

- Nov 11, 2004

- Messages

- 18,008 (2.44/day)

- Location

- Sweden

| System Name | Overlord Mk MLI |

|---|---|

| Processor | AMD Ryzen 7 7800X3D |

| Motherboard | Gigabyte X670E Aorus Master |

| Cooling | Noctua NH-D15 SE with offsets |

| Memory | 32GB Team T-Create Expert DDR5 6000 MHz @ CL30-34-34-68 |

| Video Card(s) | Gainward GeForce RTX 4080 Phantom GS |

| Storage | 1TB Solidigm P44 Pro, 2 TB Corsair MP600 Pro, 2TB Kingston KC3000 |

| Display(s) | Acer XV272K LVbmiipruzx 4K@160Hz |

| Case | Fractal Design Torrent Compact |

| Audio Device(s) | Corsair Virtuoso SE |

| Power Supply | be quiet! Pure Power 12 M 850 W |

| Mouse | Logitech G502 Lightspeed |

| Keyboard | Corsair K70 Max |

| Software | Windows 10 Pro |

| Benchmark Scores | https://valid.x86.fr/yfsd9w |

Zero ASIC, a semiconductor startup, came out of stealth today to announce early access to its one-of-a-kind ChipMaker platform, demonstrating a number of world firsts:

"Custom Application Specific Integrated Circuits (ASICs) offer 10-100X cost and energy advantage over commercial off the shelf (COTS) devices, but the enormous development cost makes ASICs non-viable for most applications," said Andreas Olofsson, CEO and founder of Zero ASIC. "To build the next wave of world changing silicon devices, we need to reduce the barrier to ASICs by orders of magnitude. Our mission at Zero ASIC is to make ordering an ASIC as easy as ordering catalog parts from an electronics distributor."

ChipMaker Platform

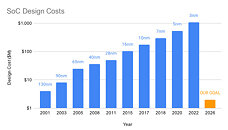

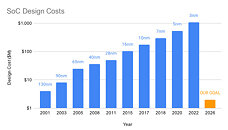

Traditional chip design costs over $100M and takes expert teams 2-3 years to go from concept to production. Chiplet-based design offers a compelling solution to both the time and cost problem of custom ASICs by hiding all the complexities of circuit design inside a reusable validated chiplet. Zero ASIC has gone one step further by creating a platform that enables automated design, validation, and assembly of System-in-Packages from a catalog of known good chiplets. The company's ChipMaker web based tools allows users to test out their custom designs quickly and accurately before ordering physical devices, using cloud FPGAs to implement the RTL source code of each chiplet in a custom SoC.

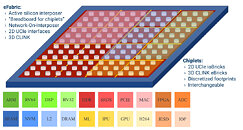

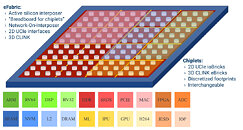

eFabric Active Interposer

Existing 2D/2.5D chiplet design approaches are fundamentally limited in shoreline bandwidth, wiring distances, and flexibility. To address these problems, Zero ASIC has developed eFabric, an active grid-like 3D interposer that improves die-to-die communication efficiency and composability. The eFabric supports integration of ultra-critical processing blocks using 3D attached eBrick chiplets and integration of off-package IO functions using 2D attached UCIe based ioBrick chiplets. The eFabric architecture enables unprecedented chiplet-based performance levels and flexibility:

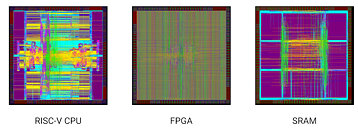

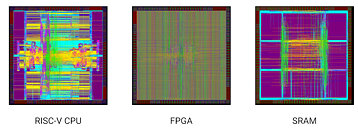

eBrick 3D Chiplets

To enable plug-and-play chiplet composability, Zero ASIC has created a complete set of electrical and mechanical 3D chiplet standards specifications. The effectiveness of these standards have been demonstrated through the design of a number of interoperable 2 mm x 2 mm chiplets called eBricks:

Target Markets and Availability

Zero ASIC's composable chiplet ASICs are ideally suited for a diverse set of energy and supply chain challenged applications including robotics, automotive safety, aerospace and defense, 5G/6G communication, test and measurement, software defined radio, smart manufacturing, medical diagnostics, and high performance computing. The ChipMaker design and emulation platform can be accessed immediately at zeroasic.com. Zero ASIC will be showing live demonstrations of the ChipMaker platform at the Open Compute Platform Summit (Open Chiplet Economy Center) October 17-19, in San Jose, CA. Customized ASICs sampling in Q3 2024.

View at TechPowerUp Main Site | Source

- 3D chiplet composability enabling billions of new silicon products

- Fully automated no-code chiplet-based chip design

- Zero install interactive RTL-based chip emulation

- Roadmap to 100X reduction in chip development costs

"Custom Application Specific Integrated Circuits (ASICs) offer 10-100X cost and energy advantage over commercial off the shelf (COTS) devices, but the enormous development cost makes ASICs non-viable for most applications," said Andreas Olofsson, CEO and founder of Zero ASIC. "To build the next wave of world changing silicon devices, we need to reduce the barrier to ASICs by orders of magnitude. Our mission at Zero ASIC is to make ordering an ASIC as easy as ordering catalog parts from an electronics distributor."

ChipMaker Platform

Traditional chip design costs over $100M and takes expert teams 2-3 years to go from concept to production. Chiplet-based design offers a compelling solution to both the time and cost problem of custom ASICs by hiding all the complexities of circuit design inside a reusable validated chiplet. Zero ASIC has gone one step further by creating a platform that enables automated design, validation, and assembly of System-in-Packages from a catalog of known good chiplets. The company's ChipMaker web based tools allows users to test out their custom designs quickly and accurately before ordering physical devices, using cloud FPGAs to implement the RTL source code of each chiplet in a custom SoC.

eFabric Active Interposer

Existing 2D/2.5D chiplet design approaches are fundamentally limited in shoreline bandwidth, wiring distances, and flexibility. To address these problems, Zero ASIC has developed eFabric, an active grid-like 3D interposer that improves die-to-die communication efficiency and composability. The eFabric supports integration of ultra-critical processing blocks using 3D attached eBrick chiplets and integration of off-package IO functions using 2D attached UCIe based ioBrick chiplets. The eFabric architecture enables unprecedented chiplet-based performance levels and flexibility:

- Billions of unique System-In-Package assembly options

- 512 Gb/s/mm on-fabric bisection bandwidth

- 128 Gb/s/mm chiplet 2D bandwidth

- 128 Gb/s/mm² chiplet 3D bandwidth

- <0.1 pJ/bit 3D interconnect energy efficiency

eBrick 3D Chiplets

To enable plug-and-play chiplet composability, Zero ASIC has created a complete set of electrical and mechanical 3D chiplet standards specifications. The effectiveness of these standards have been demonstrated through the design of a number of interoperable 2 mm x 2 mm chiplets called eBricks:

- Quad-core RISC-V Linux capable dual-issue processor

- 5 K LUT embedded FPGA

- 3 MB SRAM -3 TOPS machine learning accelerator

Target Markets and Availability

Zero ASIC's composable chiplet ASICs are ideally suited for a diverse set of energy and supply chain challenged applications including robotics, automotive safety, aerospace and defense, 5G/6G communication, test and measurement, software defined radio, smart manufacturing, medical diagnostics, and high performance computing. The ChipMaker design and emulation platform can be accessed immediately at zeroasic.com. Zero ASIC will be showing live demonstrations of the ChipMaker platform at the Open Compute Platform Summit (Open Chiplet Economy Center) October 17-19, in San Jose, CA. Customized ASICs sampling in Q3 2024.

View at TechPowerUp Main Site | Source