Intel

attempted on-package DRAM in 2014, but never shipped, IIRC: unfortunately typical for Intel, but Intel will gladly explain the benefits of on-package DRAM to you:

Intel sold Tablet Atoms with on-package DRAM in 2014. And I can even attest for this personally as my Dell Venue 8 Pro I used at that time had the chip. I took it apart few years later once I stopped using it due to screen damage and there's no DRAM chip anywhere. Of course people don't remember as for Tablets on-package DRAM is granted while for their main line of chips it's some magic.

The first on-package Atom was even before that with the Smartphone oriented Medfield in 2012:

https://www.anandtech.com/show/5365/intels-medfield-atom-z2460-arrive-for-smartphones/1

Meteorlake will also have some on-package DRAM variants, but unlike Lunar Lake it doesn't claim to be a big advance in mobility, so it'll be only available in certain variants while for Lunar Lake it'll have it for all.

Intel preps Meteor Lake processors with integrated LPDDR5X

www.tomshardware.com

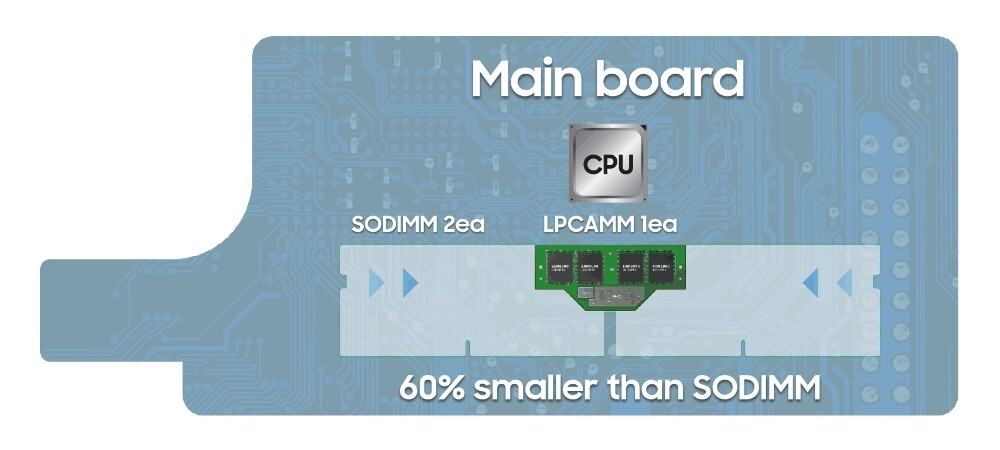

Given that LPCAMM is coming next year, it'd be nice to move toward more configurable laptops and not less.

Samsung Electronics, a world leader in advanced memory technology, today announced that it has developed the industry's first Low Power Compression Attached Memory Module (LPCAMM) form factor, which is expected to transform the DRAM market for PCs and laptops - and potentially even data centers...

www.techpowerup.com

LPCAMM is nowhere near low power or compact enough for what's going in Lunar Lake. It will be more than before sure.

One aspect might be specialization of the nodes. Intel 4 is frequency-optimized, so it's the logical choice for Meteor Lake's CPU tile. Intel 3 can be density-optimized, making it the logical choice for the GPU and SoC tiles, but Intel 3 isn't ready and TSMC N5 and N6 are, and as it happens these are being used for the GPU and SoC tiles of Meteor Lake. Intel 20A will be frequency-optimized and Intel 18A will be able to be density-optimized.

I'm not sure why Arrow Lake would have TSMC parts. It seems to me that an Intel 20A CPU tile with Intel 3 GPU and SoC tiles ought to do quite well if 3 and 20A can be produced in enough quantity. And if Lunar Lake has access to all these and Intel 18A, then there oughtn't be a need for TSMC in that product.

Intel 4 doesn't have enough libraries for Lunar Lake, period. Not fully sure about Intel 3, but they admit that they won't really get ahead until 18A, and Intel 3 is going to be using a ton of wafers because both E and P core Xeons are going to be using them and they are all very large dies. Granite Rapids-SP has two compute tiles with over 500mm2 size, while -AP version has three. Sierra Forest-SP has 1x 500mm2+ die, while -AP has 2x.

20A is same as Intel 4 in that it doesn't have enough libraries. If Intel keeps using TSMC for main chip compute tile by 18A, then it's a problem, but until then, there are legitimate reasons for doing what they are doing. When it comes to Intel 3 and 18A being foundry-oriented process, the reason is same. Only those two have all the libraries required, while 4 and 20A contains enough blocks for CPU to rapidly iterate to next generation. With Lunar Lake coming sometime next year and 18A not being production-ready until end of next year, 18A is a no-go.

Lunar Lake was conceived around the time when Apple abandoned Intel, and future of their manufacturing was murky. But as of right now multiple reports state manufacturing is now going full steam while design team is still meh. The design team had been hiding behind massive process lead, and this loss exposes them.

Gelsinger is bringing changes and new metrics to bring accountability for the design team, so hopefully they'll do better. The design team was doing appalling things such as directing the process team to change the metrics to fit their needs, rather than working with what they have. Now, the goal is the design team is essentially treated little more than 3rd party.

If 4. 3 and 20A will be on time ind successful, they should have plenty of free capacity in 10/7nm fabs. Is it better to use them to produce for 3rd parties and produce their own at TSMC? I think it would be better to convert these fabs to 18A and produce their own CPUs.

Leaked slides show that I/O die for Granite Rapids and Sierra Forest use Intel 7, while compute tile uses Intel 3. As I said the compute tiles for both are over 500mm2. Rough analysis got 510mm2. So it's in the ballpark of 500mm2. Yea they have three compute size variants but regardless these tiles are massive.

The Intel 3 and 18A is more than a plus. It's more like 10nm SF and Intel 7, but without the density loss SF and 7 brought. The numerous plusses in 14nm only brought about 4-5% gains, while 3 gains 18% alone, and will have density advantage for high performance libraries(so for successors to Meteorlake), while 3 has full set of libraries for I/O, GPU, CPU, and so on, while 4 is bare minimum.