- Joined

- Oct 9, 2007

- Messages

- 47,260 (7.54/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

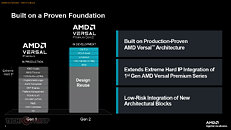

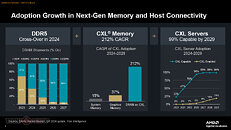

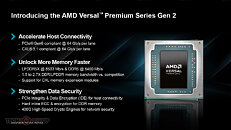

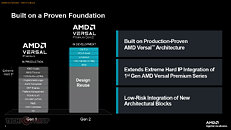

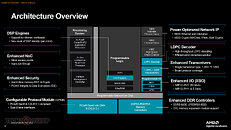

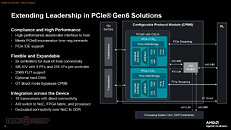

AMD on Tuesday released its flagship FPGA series, and possibly its most important product launch after the company's Xilinx acquisition, the Versal Premium Series Gen 2 SoC. It's hard to call this an FPGA, much in the same way as it's hard to call a modern processor "a CPU," there are many integrated devices, platform interfaces, and application-specific accelerators, and much in the same way, the Versal Premium Series Gen 2 is marketed as an "adaptive SoC," rather than a really powerful FPGA. Speaking of I/O, this is AMD's first product to implement PCI-Express Gen 6 and CXL 3.1.

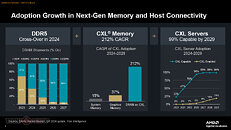

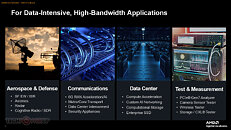

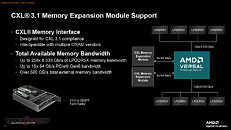

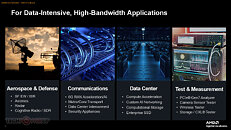

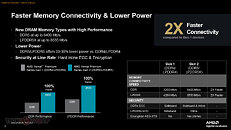

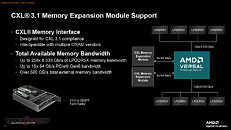

There's no host platform that currently support these standards—neither EPYC "Turin" nor Xeon 6 "Granite Rapids," but it goes to show that the chip is future-ready and can put the new I/O standards to use. The chip is designed to be implemented as a standalone SoC, and so it supports both DDR5 RDIMMs and LPDDR5X, giving end-users the flexibility to go with the two vastly different memory standards depending on what their application is. These capabilities make the Versal Premium Series Gen 2 well-suited for demanding applications in sectors like data centers, communications, test and measurement, aerospace, and defense, where high-speed data processing is critical.

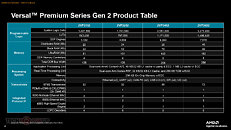

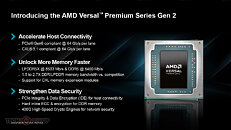

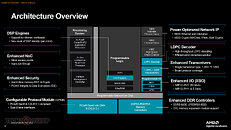

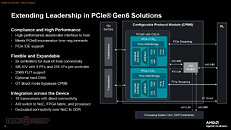

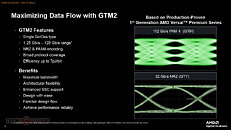

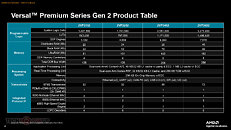

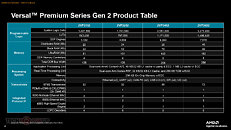

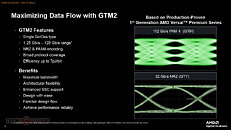

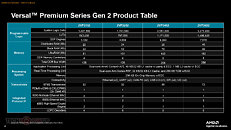

The main feature of the Versal Premium Series Gen 2 is its FPGA. Put short, think of an FPGA as a sea of transistors that you can program to work like any logic device you want. This is different from emulation, because the FPGA performs close to what an ASIC would. FPGAs are crucial when designing and prototyping ASICs, or for hardware manufacturers that have a very small production target to create the logic device they want using an FPGA (think a space agency creating an SoC for one of its interplanetary probes). The Versal Premium Series Gen 2, depending on the model, comes with anywhere between 1.40 to 3.27 million system logic cells (SLCs), 643k to 1.49 million LUTs, 3,320 to 7,616 DSP engines, 4 to 8 DDR5/LPDDR5x memory controllers, and a memory bus width ranging from 128-bit to 256-bit. I/O includes a dual PCI-Express 6.0 x8 interface (64 Gbps per lane), which converts to a CXL 3.1 interface of comparable bandwidth, and a multitude of MACs, including a 100 Gbps multirate Ethernet MAC, up to five 600 Gbps Ethernet MACs depending on the model, and a 400 Gbps high-speed crypto engine.

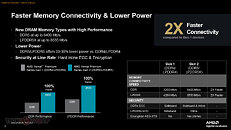

In addition to faster connectivity, Versal Premium Series Gen 2 includes enhanced security features. It is the first FPGA to integrate PCIe Integrity and Data Encryption (IDE) directly within its hard IP, offering high-level security for data in transit. It also incorporates 400 Gbps Crypto Engines, which support accelerated, secure data transmission. AMD has embedded encryption into the platform's DDR memory controllers, ensuring data at rest is also protected. Development tools for the Versal Premium Gen 2 will be available in 2025, with production expected in 2026. With these innovations, AMD's Versal Premium Series Gen 2 aims to redefine adaptive computing for industries seeking scalable, high-performance, and secure data handling solutions.

AMD will begin sampling and releasing development tools of the Versal Premium Series Gen 2 in 2025, while taking orders. Production of the SoC should commence in 2026—now you know why it comes with a PCIe Gen 6 interface.

For more information, visit the product page.

The complete slide-deck from AMD follows.

View at TechPowerUp Main Site

There's no host platform that currently support these standards—neither EPYC "Turin" nor Xeon 6 "Granite Rapids," but it goes to show that the chip is future-ready and can put the new I/O standards to use. The chip is designed to be implemented as a standalone SoC, and so it supports both DDR5 RDIMMs and LPDDR5X, giving end-users the flexibility to go with the two vastly different memory standards depending on what their application is. These capabilities make the Versal Premium Series Gen 2 well-suited for demanding applications in sectors like data centers, communications, test and measurement, aerospace, and defense, where high-speed data processing is critical.

The main feature of the Versal Premium Series Gen 2 is its FPGA. Put short, think of an FPGA as a sea of transistors that you can program to work like any logic device you want. This is different from emulation, because the FPGA performs close to what an ASIC would. FPGAs are crucial when designing and prototyping ASICs, or for hardware manufacturers that have a very small production target to create the logic device they want using an FPGA (think a space agency creating an SoC for one of its interplanetary probes). The Versal Premium Series Gen 2, depending on the model, comes with anywhere between 1.40 to 3.27 million system logic cells (SLCs), 643k to 1.49 million LUTs, 3,320 to 7,616 DSP engines, 4 to 8 DDR5/LPDDR5x memory controllers, and a memory bus width ranging from 128-bit to 256-bit. I/O includes a dual PCI-Express 6.0 x8 interface (64 Gbps per lane), which converts to a CXL 3.1 interface of comparable bandwidth, and a multitude of MACs, including a 100 Gbps multirate Ethernet MAC, up to five 600 Gbps Ethernet MACs depending on the model, and a 400 Gbps high-speed crypto engine.

In addition to faster connectivity, Versal Premium Series Gen 2 includes enhanced security features. It is the first FPGA to integrate PCIe Integrity and Data Encryption (IDE) directly within its hard IP, offering high-level security for data in transit. It also incorporates 400 Gbps Crypto Engines, which support accelerated, secure data transmission. AMD has embedded encryption into the platform's DDR memory controllers, ensuring data at rest is also protected. Development tools for the Versal Premium Gen 2 will be available in 2025, with production expected in 2026. With these innovations, AMD's Versal Premium Series Gen 2 aims to redefine adaptive computing for industries seeking scalable, high-performance, and secure data handling solutions.

AMD will begin sampling and releasing development tools of the Versal Premium Series Gen 2 in 2025, while taking orders. Production of the SoC should commence in 2026—now you know why it comes with a PCIe Gen 6 interface.

For more information, visit the product page.

The complete slide-deck from AMD follows.

View at TechPowerUp Main Site