- Joined

- Oct 9, 2007

- Messages

- 47,571 (7.46/day)

- Location

- Dublin, Ireland

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

Some of the first images of a de-lidded Intel Core Ultra 9 285K "Arrow Lake-S" processor surfaced on the web, confirming a disaggregated chiplet-based processor design. Intel pivoted to chiplet based processors with its Core Ultra "Meteor Lake," allowing it to build specific IP blocks of the processor on different foundry nodes, ensuring the ones that don't need the most advanced nodes can make do with slightly older ones, thereby maximizing Intel's yields for that advanced node. The die shot reveals a similar level of disaggregation to "Meteor Lake" than that of the more recent Core Ultra 200V "Lunar Lake" mobile processor.

With "Lunar Lake," Intel had re-aggregated a few things. "Lunar Lake" only has two tiles—SoC tile and I/O tile. The 3 nm SoC tile contains the CPU complex, a large iGPU, and a large 40 TOPS-class NPU, all sharing die-space with the memory controllers, and PCIe root complex. The smaller 6 nm I/O tile contains the PHYs of the various I/O interfaces. The "Arrow Lake" chip appears to have a similar degree of disaggregation as "Meteor Lake." We can spot at least five tiles sitting on top of the Foveros base tile. The picture has no annotation for the various tiles, but recent reports by Moore's Law is Dead and Jay Kihn shed some light on what these could be.

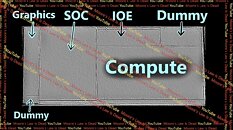

The MLID report says that there will be a Compute tile containing the CPU cores, an SoC tile, a Graphics tile, a breakout I/O tile, and some dummy tiles that provide structural reinforcement, giving the chip a rectangular form. The Jay Kihn leak points to the Compute tile containing the P-cores and E-core clusters arranged in a conventional ring-bus, sharing an L3 cache, similar to how things are in the Compute tile of "Meteor Lake." This tile contains eight "Lion Cove" P-cores, each with 3 MB of dedicated L2 cache (we know this from the Lunar Lake technical deep-dive), and four "Skymont" E-core clusters, each with 4 MB of shared L2 cache. All CPU cores share a 36 MB L3 cache.

The Compute tile talks to the SoC tile, which contains the DDR5 memory controllers, the PCIe Gen 5 root-complex, security processor, the display controller, and the media acceleration engine. There's also an "AI complex," which could very well be an NPU. It remains to be seen if this is the larger NPU 4 carried over from "Lunar Lake," which meets Microsoft Copilot+ requirements. The SoC tile puts out some I/O, such as the DDR5 memory, and a portion of the PCIe, but relies on a breakout I/O tile to put out more PCIe connectivity, and integrated Thunderbolt.

Lastly, there's the Graphics tile, which contains the iGPU, mainly the Xe cores and all the hardware the iGPU needs in the graphics rendering pipeline, including an L3 cache of its own. The display controllers and media accelerators are located in the SoC tile, and the display I/O is located in the breakout I/O tile. Looking at the size of the Graphics tile, if we were to guess, the desktop version of "Arrow Lake" likely won't have a very large iGPU, it may only have up to two Xe cores. In contrast, "Lunar Lake" has a large iGPU with 8 Xe cores, because the idea behind "Lunar Lake" is thin-and-light notebooks without discrete graphics.

View at TechPowerUp Main Site | Source

With "Lunar Lake," Intel had re-aggregated a few things. "Lunar Lake" only has two tiles—SoC tile and I/O tile. The 3 nm SoC tile contains the CPU complex, a large iGPU, and a large 40 TOPS-class NPU, all sharing die-space with the memory controllers, and PCIe root complex. The smaller 6 nm I/O tile contains the PHYs of the various I/O interfaces. The "Arrow Lake" chip appears to have a similar degree of disaggregation as "Meteor Lake." We can spot at least five tiles sitting on top of the Foveros base tile. The picture has no annotation for the various tiles, but recent reports by Moore's Law is Dead and Jay Kihn shed some light on what these could be.

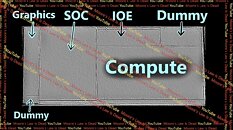

The MLID report says that there will be a Compute tile containing the CPU cores, an SoC tile, a Graphics tile, a breakout I/O tile, and some dummy tiles that provide structural reinforcement, giving the chip a rectangular form. The Jay Kihn leak points to the Compute tile containing the P-cores and E-core clusters arranged in a conventional ring-bus, sharing an L3 cache, similar to how things are in the Compute tile of "Meteor Lake." This tile contains eight "Lion Cove" P-cores, each with 3 MB of dedicated L2 cache (we know this from the Lunar Lake technical deep-dive), and four "Skymont" E-core clusters, each with 4 MB of shared L2 cache. All CPU cores share a 36 MB L3 cache.

The Compute tile talks to the SoC tile, which contains the DDR5 memory controllers, the PCIe Gen 5 root-complex, security processor, the display controller, and the media acceleration engine. There's also an "AI complex," which could very well be an NPU. It remains to be seen if this is the larger NPU 4 carried over from "Lunar Lake," which meets Microsoft Copilot+ requirements. The SoC tile puts out some I/O, such as the DDR5 memory, and a portion of the PCIe, but relies on a breakout I/O tile to put out more PCIe connectivity, and integrated Thunderbolt.

Lastly, there's the Graphics tile, which contains the iGPU, mainly the Xe cores and all the hardware the iGPU needs in the graphics rendering pipeline, including an L3 cache of its own. The display controllers and media accelerators are located in the SoC tile, and the display I/O is located in the breakout I/O tile. Looking at the size of the Graphics tile, if we were to guess, the desktop version of "Arrow Lake" likely won't have a very large iGPU, it may only have up to two Xe cores. In contrast, "Lunar Lake" has a large iGPU with 8 Xe cores, because the idea behind "Lunar Lake" is thin-and-light notebooks without discrete graphics.

View at TechPowerUp Main Site | Source