TSMC Expands Advanced Technology Leadership with N4P Process

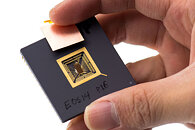

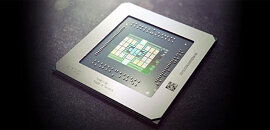

TSMC today introduced its N4P process, a performance-focused enhancement of the 5-nanometer technology platform. N4P joins the industry's most advanced and extensive portfolio of leading-edge technology processes. With N5, N4, N3 and the latest addition of N4P, TSMC customers will have multiple and compelling choices for power, performance, area, and cost for its products.

As the third major enhancement of TSMC's 5 nm family, N4P will deliver an 11% performance boost over the original N5 technology and a 6% boost over N4. Compared to N5, N4P will also deliver a 22% improvement in power efficiency as well as a 6% improvement in transistor density. In addition, N4P lowers process complexity and improves wafer cycle time by reducing the number of masks. N4P demonstrates TSMC's pursuit and investment in continuous improvement of our process technologies.

As the third major enhancement of TSMC's 5 nm family, N4P will deliver an 11% performance boost over the original N5 technology and a 6% boost over N4. Compared to N5, N4P will also deliver a 22% improvement in power efficiency as well as a 6% improvement in transistor density. In addition, N4P lowers process complexity and improves wafer cycle time by reducing the number of masks. N4P demonstrates TSMC's pursuit and investment in continuous improvement of our process technologies.