Intel Takes Big Strides in Chip Packaging Tech

Intel's silicon fabrication technological edge over TSMC and Samsung may have buckled, but the company appears to have made big advances in chip packaging. We've known for some time about EMIB (embedded multi-die interconnect bridge), Intel's cost-effective alternative to using full-fledged interposers; and Foveros heterogenous multi-die packaging; but the company has apparently invented more forms of 3-D chip stacking, as detailed by a WikiChip Fuse report. By leveraging ODI (omni-directional interconnect), an evolutionary next-step to EMIB and Foveros, Intel is able to stack multiple chips above the fiberglass substrate, above each other; and inside indentations and cavities of the substrate.

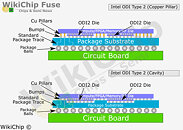

ODI consists of EMIB-like silicon dies that enable high-density wiring between two dies (think a GPU and its memory stack, or an SoC and core-logic); and copper poles that serve as extensions of the bumps of silicon dies getting to the substrate. There are two types of ODI. Type-1 refers to an interconnect running between two top dies, with the ODI die sitting between them and the substrate at the point of the inter-die connection region; while copper poles compensate for the Z-height difference. In scenarios without copper poles, chip designers can opt for substrates with cavities (regions with fewer layers), where the ODI die can be slotted in. In type-2 ODI, the interconnect die sits completely under a top die, providing high-density wiring either between two regions of the same die, or between two dies. The two types can be mixed and matched to achieve extremely complex MCMs.

ODI consists of EMIB-like silicon dies that enable high-density wiring between two dies (think a GPU and its memory stack, or an SoC and core-logic); and copper poles that serve as extensions of the bumps of silicon dies getting to the substrate. There are two types of ODI. Type-1 refers to an interconnect running between two top dies, with the ODI die sitting between them and the substrate at the point of the inter-die connection region; while copper poles compensate for the Z-height difference. In scenarios without copper poles, chip designers can opt for substrates with cavities (regions with fewer layers), where the ODI die can be slotted in. In type-2 ODI, the interconnect die sits completely under a top die, providing high-density wiring either between two regions of the same die, or between two dies. The two types can be mixed and matched to achieve extremely complex MCMs.