Friday, June 11th 2021

AMD Shares New Details on Their 3D V-Cache Tech for Zen 3+

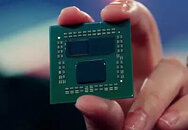

AMD via its official YouTube has shared a video that goes into slightly more detail on their usage of V-Cache on the upcoming Zen 3+ CPUs. Firstly demoed to the public on AMD's Computex 2021 event, the 3D V-Cache leverages TSMC's SoIC stacking technology, which enables silicon developments along the Z axis, instead of the more usual footprint increase along the X axis. The added 3D V-Cache, which was shown in Computex as being deployed in a prototype Ryzen 9 5900X 12-core CPU, adds 64 MB of L3 cache to each CCX (the up-to-eight-cores core complex on AMD's latest Zen design), basically tripling the amount of L3 cache available for the CPU. This, in turn, was shown to increase FPS in games quite substantially (somewhere around 15%), as games in particular are sensitive to this type of CPU resources.

The added information explains that there is no usage of microbumps - instead, there is a perfect alignment between the bottom layer (with the CCX) and the top layer (the L3 cache) which enables the bonding process to occur naturally via the TSVs (Through Silicon Vias) already present in the silicon, in a zero-gap manner, between both halves of the CPU-cache sandwich. To enable this, AMD flipped the CCX upside down (the core complex now faces the bottom of the chip, instead of the top), shaved 95% of the silicon on top of the upside-down core complexes, and then attaches the 3D V-Cache chips on top of this formation. This also has the added bonus of decreasing the distance between the L3 cache and the CCX (the distance between both in the Z axis is around 1,000 times smaller than if the L3 cache was deployed in the classical X axis), which decreases power consumption, temperatures, and latency, allowing for further increases to system performance. Look after the break for the full video.

Source:

AMD

The added information explains that there is no usage of microbumps - instead, there is a perfect alignment between the bottom layer (with the CCX) and the top layer (the L3 cache) which enables the bonding process to occur naturally via the TSVs (Through Silicon Vias) already present in the silicon, in a zero-gap manner, between both halves of the CPU-cache sandwich. To enable this, AMD flipped the CCX upside down (the core complex now faces the bottom of the chip, instead of the top), shaved 95% of the silicon on top of the upside-down core complexes, and then attaches the 3D V-Cache chips on top of this formation. This also has the added bonus of decreasing the distance between the L3 cache and the CCX (the distance between both in the Z axis is around 1,000 times smaller than if the L3 cache was deployed in the classical X axis), which decreases power consumption, temperatures, and latency, allowing for further increases to system performance. Look after the break for the full video.

37 Comments on AMD Shares New Details on Their 3D V-Cache Tech for Zen 3+

I REALLY hope that Zen3+ is for AM4, as I don't like what I'm seeing with DDR5. I think it's just too early for AMD to abandon AM4 and DDR4, at least for this year.

This is the definition of success however way anybody puts it!

Either they don't yet know what "it's normal speed" will end up being, which is actually quite likely, or this prototype will end up having a lower frequency than the 5900X due to it's new "3D nature", meaning that 15% improvement might not actually be as much as it seems to be.

Ofc, that 15% @ 4 GHz is only with the 3D V-cache without anything else, so it's still possible that the new Zen 3+ CPU could still end up being 15%+ faster than the 5900X WHILE having ... say ... 400 to 500 MHz LESS frequency, depending on WHAT ELSE is being changed VS Zen 3.

Like, Zen 3+ being intended for APUs, with several improvements over Zen 3, similar to what Lucienne is for Zen 2. And 3D V-cache for high end Ryzen CPUs, those that can bear the high cost of advanced packaging and additional silicon.

Cache admittedly improves single threading since it acts like a huge page file.

Plus she could only show a prototype, you realise this isn't even a qualification sample.

It's clearly early in the production cycle ,only an idiot would show all their competitors they're full hand with enough time to do something about it that's competitive?!.

No glue, either , make's me wonder how strong that atomic flatness bonding is, Many of us have used standard set guages , sets of metal blocks produced to a very high standard that are used to measure gaps via building up different sizes via a similar bond, they're not hard to pull back apart, though obviously the interposer and IHS will easily clamp it into a package.

It definitely wasn't a personal dig.

Now imagine GPU gluing like that.

There must be some kind of electrochemical process that actually bonds copper to copper. TSMC and other manufacturers won't tell much. I found an older document here, it gives some hints like "During chip stacking, inter-metallic compounds (IMCs) are formed" and "The planar bumping system described above is formed by a metallurgical reaction" (and Sn or Cu/Sn is present too, not just pure Cu). Another option is this ... maybe (vacuum, plasma, high pressure, sharks with lasers, etc).

@Raevenlord describes this in an optimistic way as "the bonding process to occur naturally via the TSVs" but this can't be the whole truth.

No bumps no sacrificial deforming bump nothing just stiction ( had to look that up)similar to gauge blocks

They're also ground so thin as to technically Be flexible.

I agree on clamping pressure, it would have to work sans that and the prototype clearly demonstrated that.

So I will concede it's not going to be held together via that after some thought.

But no, just stiction, :) new word woo :).

I hope it's not some kind of thermal compromise where the CPU will clock down when under high use.

We'll have to wait and see ...