CPUs or GPUs? Ryzen 3000 series up to 16 cores or keeping their eight? Support for raytracing? Navi or die-shrunk Vega for consumer graphics? The questions around AMD's plans for 2019 are still very much in the open, but AMD's Lisa Su's impending livestream should field the answers to many of these questions, so be sure to watch the full livestream, happening in just a moment.

You can find the

live stream here, at YouTube.

18:33 UTC: Looking forward, Lisa mentioned a few technology names without giving additional details: "... when you're talking about future cores, Zen 2, Zen 3, Zen 4, Zen 5, Navi, we're putting all of these architectures together, in new ways".

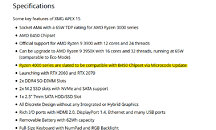

18:20 UTC: New Ryzen 3rd generation processors have been teased. The upcoming processors are based on Zen 2, using 7 nanometer technology. AMD showed a live demo of Forza Horizon 4, using Ryzen third generation, paired with Radeon Vega VII, which is running "consistently over 100 FPS at highest details at 1080p resolution". A second demo, using Cinebench, pitted an 8-core/16-thread Ryzen 3rd generation processor against the Intel Core i9-9900K. The Ryzen CPU was "not final frequency, an early sample". Ryzen achieved a score of 2057 using 135 W, while Intel achieved a score of 2040 using 180 W.. things are looking good for Ryzen 3rd generation indeed. Lisa also confirmed that next-gen Ryzen will support PCI-Express 4.0, which doubles the bandwidth per lane over PCI-Express 3.0. Ryzen third generation will run on the same AM4 infrastructure as current Ryzen; all existing users of Ryzen can simply upgrade to the new processors, when they launch in the middle of 2019 (we think Computex).

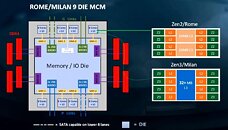

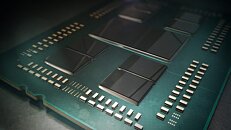

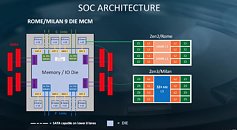

Ryzen third generation uses a chiplet design. The smaller die on the right contains 8-cores/16-threads using 7 nanometer technology. The larger die on the left is the IO die, which consists of things like the memory controller and PCI-Express connectivity, to shuffle data between the CPU core die and the rest of the system.