Intel "Alder Lake-S" Due for September 2021

2021 is shaping up to be a big year for Intel in the DIY desktop space, with the company preparing to launch not one, but two generations of desktop processors. Having announced them in January, the 11th Gen Core "Rocket Lake-S" desktop processors in the LGA1200 package, will release to market in March, with the company claiming a restoration in gaming performance leadership away from AMD's Ryzen 5000 series. Sources tell Uniko's Hardware that the company will announce its 12th Gen successor, the Core "Alder Lake-S" in September 2021.

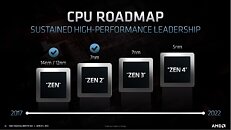

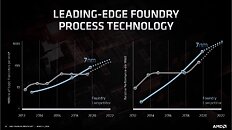

"Alder Lake-S" will be Intel's first mainstream desktop processor built on its new 10 nm SuperFin silicon fabrication process. The chip is expected to be a "hybrid" processor, combining an equal number of larger "Golden Cove" cores, and smaller "Gracemont" cores, to offer significantly improved energy efficiency. Built in the new Socket LGA1700 package, "Alder Lake-S" is expected to feature more general-purpose SoC connectivity than LGA1200 chips. It will also herald new platform standards, such as DDR5 memory and possibly even mainstreaming of ATX12VO. The processor will launch alongside new Intel 600-series chipset. AMD's response is expected to be the "Zen 4" microarchitecture, a new silicon built on the 5 nm process, and the new AM5 socket that introduces DDR5 memory support.

"Alder Lake-S" will be Intel's first mainstream desktop processor built on its new 10 nm SuperFin silicon fabrication process. The chip is expected to be a "hybrid" processor, combining an equal number of larger "Golden Cove" cores, and smaller "Gracemont" cores, to offer significantly improved energy efficiency. Built in the new Socket LGA1700 package, "Alder Lake-S" is expected to feature more general-purpose SoC connectivity than LGA1200 chips. It will also herald new platform standards, such as DDR5 memory and possibly even mainstreaming of ATX12VO. The processor will launch alongside new Intel 600-series chipset. AMD's response is expected to be the "Zen 4" microarchitecture, a new silicon built on the 5 nm process, and the new AM5 socket that introduces DDR5 memory support.