- Joined

- Oct 9, 2007

- Messages

- 47,291 (7.53/day)

- Location

- Hyderabad, India

| System Name | RBMK-1000 |

|---|---|

| Processor | AMD Ryzen 7 5700G |

| Motherboard | ASUS ROG Strix B450-E Gaming |

| Cooling | DeepCool Gammax L240 V2 |

| Memory | 2x 8GB G.Skill Sniper X |

| Video Card(s) | Palit GeForce RTX 2080 SUPER GameRock |

| Storage | Western Digital Black NVMe 512GB |

| Display(s) | BenQ 1440p 60 Hz 27-inch |

| Case | Corsair Carbide 100R |

| Audio Device(s) | ASUS SupremeFX S1220A |

| Power Supply | Cooler Master MWE Gold 650W |

| Mouse | ASUS ROG Strix Impact |

| Keyboard | Gamdias Hermes E2 |

| Software | Windows 11 Pro |

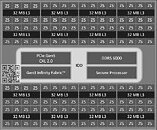

AMD's upcoming server processor, the 5th Gen EPYC "Turin," has been pictured as an engineering sample is probably being evaluated by the company's data-center or cloud customers. The processor has a mammoth core-count of 192-core/384-thread in its high-density cloud-focused variant that uses "Zen 5c" CPU cores. Its regular version that uses larger "Zen 5" cores that can sustain higher clock speeds, also comes with a fairly high core-count of 128-core/256-thread, up from the 96-core/192-thread of the "Zen 4" based EPYC "Genoa."

The EPYC "Turin" server processor based on "Zen 5" comes with an updated sIOD (server I/O die), surrounded by as many as 16 CCDs (CPU complex dies). AMD is expected to build these CCDs on the TSMC N4P foundry node, which is a more advanced version of the TSMC N4 node the company currently uses for its "Phoenix" client processors, and the TSMC N5 node it uses for its "Zen 4" CCD. TSMC claims that the N4P node offers an up to 22% improvement in power efficiency over N5, as well as a 6% increase in transistor density. Each of the "Zen 5" CCDs is confirmed to have 8 CPU cores sharing 32 MB L3 cache memory. A total of 16 such CCDs add up to the processor's 128-core/256-thread number. The high-density "Turin" meant for cloud data-centers, is a whole different beast.

The "Turin" processor uses 12 "Zen 5c" CCDs. Much like "Zen 4c" is to "Zen 4," the "Zen 5c" is a physically compacted version of the larger "Zen 5" core that has the same ISA (instruction sets) and IPC, but typically runs at lower clock speeds than the regular "Zen 5" cores. It's meant for high core-count processors. The high-density "Turin" MCM has the same sIOD as the regular "Turin," but with 12 "Zen 5c" CCDs. Each CCD has 16 "Zen 5c" cores share a 32 MB L3 cache. This is interesting—if you recall, the current "Zen 4c" CCD has two CCX (CPU core complexes) that each has 8 "Zen 4c" cores share a 16 MB L3 cache. The "Zen 5c" CCD doubles the total addressable L3 cache.

View at TechPowerUp Main Site | Source

The EPYC "Turin" server processor based on "Zen 5" comes with an updated sIOD (server I/O die), surrounded by as many as 16 CCDs (CPU complex dies). AMD is expected to build these CCDs on the TSMC N4P foundry node, which is a more advanced version of the TSMC N4 node the company currently uses for its "Phoenix" client processors, and the TSMC N5 node it uses for its "Zen 4" CCD. TSMC claims that the N4P node offers an up to 22% improvement in power efficiency over N5, as well as a 6% increase in transistor density. Each of the "Zen 5" CCDs is confirmed to have 8 CPU cores sharing 32 MB L3 cache memory. A total of 16 such CCDs add up to the processor's 128-core/256-thread number. The high-density "Turin" meant for cloud data-centers, is a whole different beast.

The "Turin" processor uses 12 "Zen 5c" CCDs. Much like "Zen 4c" is to "Zen 4," the "Zen 5c" is a physically compacted version of the larger "Zen 5" core that has the same ISA (instruction sets) and IPC, but typically runs at lower clock speeds than the regular "Zen 5" cores. It's meant for high core-count processors. The high-density "Turin" MCM has the same sIOD as the regular "Turin," but with 12 "Zen 5c" CCDs. Each CCD has 16 "Zen 5c" cores share a 32 MB L3 cache. This is interesting—if you recall, the current "Zen 4c" CCD has two CCX (CPU core complexes) that each has 8 "Zen 4c" cores share a 16 MB L3 cache. The "Zen 5c" CCD doubles the total addressable L3 cache.

View at TechPowerUp Main Site | Source