Industry Leaders Join Forces to Promote New High-Performance Interconnect

A group of leading technology companies today announced the Gen-Z Consortium, an industry alliance working to create and commercialize a new scalable computing interconnect and protocol. This flexible, high-performance memory semantic fabric provides a peer-to-peer interconnect that easily accesses large volumes of data while lowering costs and avoiding today's bottlenecks. The alliance members include AMD, ARM, Cavium Inc., Cray, Dell EMC, Hewlett Packard Enterprise (HPE), Huawei, IBM, IDT, Lenovo, Mellanox Technologies, Micron, Microsemi, Red Hat, Samsung, Seagate, SK hynix, Western Digital Corporation, and Xilinx.

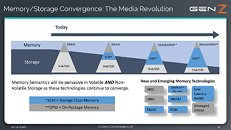

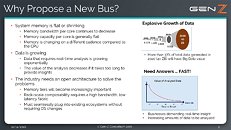

Modern computer systems have been built around the assumption that storage is slow, persistent and reliable, while data in memory is fast but volatile. As new storage class memory technologies emerge that drive the convergence of storage and memory attributes, the programmatic and architectural assumptions that have worked in the past are no longer optimal. The challenges associated with explosive data growth, real-time application demands, the emergence of low latency storage class memory, and demand for rack scale resource pools require a new approach to data access.

Modern computer systems have been built around the assumption that storage is slow, persistent and reliable, while data in memory is fast but volatile. As new storage class memory technologies emerge that drive the convergence of storage and memory attributes, the programmatic and architectural assumptions that have worked in the past are no longer optimal. The challenges associated with explosive data growth, real-time application demands, the emergence of low latency storage class memory, and demand for rack scale resource pools require a new approach to data access.