AMD X570 Unofficial Platform Diagram Revealed, Chipset Puts out PCIe Gen 4

AMD X570 is the company's first in-house design socket AM4 motherboard chipset, with the X370 and X470 chipsets being originally designed by ASMedia. With the X570, AMD hopes to leverage new PCI-Express gen 4.0 connectivity of its Ryzen 3000 Zen2 "Matisse" processors. The desktop platform that combines a Ryzen 3000 series processor with X570 chipset is codenamed "Valhalla." A rough platform diagram like what you'd find in motherboard manuals surfaced on ChipHell, confirming several features. To maintain pin-compatibility with older generations of Ryzen processors, Ryzen 3000 has the same exact connectivity from the SoC except two key differences.

On the AM4 "Valhalla" platform, the SoC puts out a total of 28 PCI-Express gen 4.0 lanes. 16 of these are allocated to PEG (PCI-Express graphics), configurable through external switches and redrivers either as single x16, or two x8 slots. Besides 16 PEG lanes, 4 lanes are allocated to one M.2 NVMe slot. The remaining 4 lanes serve as the chipset bus. With X570 being rumored to support gen 4.0 at least upstream, the chipset bus bandwidth is expected to double to 64 Gbps. Since it's an SoC, the socket is also wired to LPCIO (SuperIO controller). The processor's integrated southbridge puts out two SATA 6 Gbps ports, one of which is switchable to the first M.2 slot; and four 5 Gbps USB 3.x ports. It also has an "Azalia" HD audio bus, so the motherboard's audio solution is directly wired to the SoC. Things get very interesting with the connectivity put out by the X570 chipset.Update May 21st: There is also information on the X570 chipset's TDP.

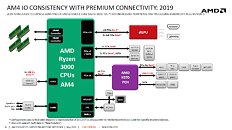

Update May 23rd: HKEPC posted what looks like an official AMD slide with a nicer-looking platform map. It confirms that AMD is going full-tilt with PCIe gen 4, both as chipset bus, and as downstream PCIe connectivity.

On the AM4 "Valhalla" platform, the SoC puts out a total of 28 PCI-Express gen 4.0 lanes. 16 of these are allocated to PEG (PCI-Express graphics), configurable through external switches and redrivers either as single x16, or two x8 slots. Besides 16 PEG lanes, 4 lanes are allocated to one M.2 NVMe slot. The remaining 4 lanes serve as the chipset bus. With X570 being rumored to support gen 4.0 at least upstream, the chipset bus bandwidth is expected to double to 64 Gbps. Since it's an SoC, the socket is also wired to LPCIO (SuperIO controller). The processor's integrated southbridge puts out two SATA 6 Gbps ports, one of which is switchable to the first M.2 slot; and four 5 Gbps USB 3.x ports. It also has an "Azalia" HD audio bus, so the motherboard's audio solution is directly wired to the SoC. Things get very interesting with the connectivity put out by the X570 chipset.Update May 21st: There is also information on the X570 chipset's TDP.

Update May 23rd: HKEPC posted what looks like an official AMD slide with a nicer-looking platform map. It confirms that AMD is going full-tilt with PCIe gen 4, both as chipset bus, and as downstream PCIe connectivity.