AI-Designed Microchips Now Outperform Human-Designed Ones

A recent Google study led by Mirhoseini et al. and published in Nature details how AI can be leveraged to improve upon semiconductor design practices currently employed - and which are the result of more than 60 years of engineering and physics studies. The paper describes a trained machine-learning 'agent' that can successfully place macro blocks, one by one, into a chip layout. This agent has a brain-inspired architecture known as a deep neural network, and is trained using a paradigm called reinforcement learning - where positive changes to a design are committed to memory as possible solutions, while negative changes are discarded, effectively allowing the neural network to build a decision-tree of sorts that's optimized every step of the way.

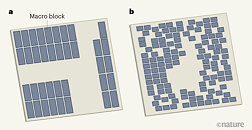

The AI isn't applied to every stage of microchip design as of yet, but that will surely change in years to come. For now, the AI is only being employed in the chip floorplanning stage of microchip production, which is actually one of the more painstaking ones. Essentially, microchip designers have to place macro blocks on their semiconductor designs - pre-made arrangements of transistors whose placement relative to one another and to the rest of the chips' components are of seminal importance for performance and efficiency targets. Remember that electric signals have to traverse different chip components to achieve a working semiconductor, and the way these are arranged in the floorplanning stage can have tremendous impact on performance characteristics of a given chip. Image A, below, showcases the tidy design a human engineer would favor - while image B showcases the apparently chaotic nature of the AI's planning.

The AI isn't applied to every stage of microchip design as of yet, but that will surely change in years to come. For now, the AI is only being employed in the chip floorplanning stage of microchip production, which is actually one of the more painstaking ones. Essentially, microchip designers have to place macro blocks on their semiconductor designs - pre-made arrangements of transistors whose placement relative to one another and to the rest of the chips' components are of seminal importance for performance and efficiency targets. Remember that electric signals have to traverse different chip components to achieve a working semiconductor, and the way these are arranged in the floorplanning stage can have tremendous impact on performance characteristics of a given chip. Image A, below, showcases the tidy design a human engineer would favor - while image B showcases the apparently chaotic nature of the AI's planning.