73

73

AMD Ryzen 9 3900XT Review

Test Setup »Architecture

The architecture is no different from the Ryzen 9 3950X or any other "Matisse," so you can click on the button below to read about it, or skip that section if you're familiar with it.Architectural Innovations Specific to Ryzen 3000XT Series

The Ryzen 3000XT family of processors are internally referred by AMD as "Matisse 2." These are almost identical to the original Ryzen 3000 "Matisse" processors based on the "Zen 2" microarchitecture, but AMD has given these processors some physical improvements. To begin with, the 8-core CCDs (compute complex dies) or "Zen 2" chiplets inside the processors are still based on TSMC N7 (the foundry's first 7 nm node), but with certain refinements. AMD claims these yields a single-digit percentage electrical improvement, which AMD used to achieve up to 200 MHz increments in maximum boost frequencies without affecting the TDP of these processors.The TDP of Ryzen 5 3600XT remains at 95 W, just like the 3600X, while the 3800XT and 3900XT both stick with 105 W TDP. AMD's decision not to include cooling solutions with the 3800XT and 3900XT have little to do with the power or thermals of these processors and more with marketing decisions. It certainly reduces AMD's bill of materials for these chips.

AMD categorically stated that this "refined" N7 node is neither N7P nor N7+. The N7P node is the successor to N7 that sticks to DUV (deep ultraviolet) lithography, but innovates in certain other areas to eke out a power improvement. N7+, on the other hand, uses EUV (extreme ultraviolet) lithography that not only yields a much higher efficiency, but also over a 20% increase in transistor density. The node AMD is building "Matisse 2" on is still N7, but with certain refinements AMD didn't elaborate in its product brief.

AMD B550 and X570 Chipsets

With premium AMD X570 chipset-based motherboards starting at $150, it's less likely that someone would pair the third-generation Ryzen 3 with it. Choosing a cheaper B450 motherboard would mean giving up on killer features such as PCIe gen 4.0. AMD hence launched the new B550 mid-range chipset. The B550 chipset lets you have PCI-Express gen 4.0 connectivity from the "Matisse" processor, while limiting general purpose PCIe downstream connectivity to gen 3.0.On a typical B550 chipset motherboard, the main PCI-Express x16 slot will be gen 4.0 if paired with a third-generation Ryzen "Matisse" processor, as would one of the board's M.2 NVMe slots that's wired to the processor. All other PCIe or M.2 slots which are wired to the B550 chipset will be gen 3.0. This way, future-proofing of the platform for next-generation graphics cards and SSDs remains intact. The B550 chipset provides up to six SATA 6 Gbps ports with AHCI and RAID capability, up to two 10 Gbps USB 3.1 gen 2 ports (in addition to four such ports put out by the "Matisse" processor), two additional USB 3.1 gen 1 ports, and six USB 2.0 ports. The platform's HDA and LPCIO buses are located on the processor.

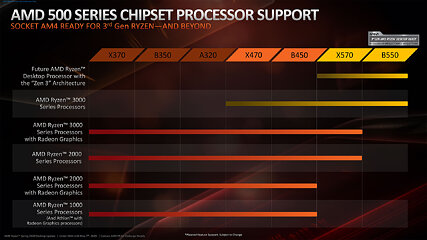

A word on compatibility. The B550 chipset only supports third-generation Ryzen "Matisse" processors as of this writing, and AMD confirmed support for next-generation processors based on the "Zen 3" architecture. You cannot pair a B550 motherboard with older Ryzen 2000/1000 processors or even the 3200G or 3400G APUs based on the older "Zen+" microarchitecture. There will be clear labeling on B550 chipset motherboard boxes to this effect.

What we like most about the B550 is its low TDP, which lets motherboard designers make do with passive heatsinks; unlike X570, which requires active fan heatsinks.

AMD delivered on its promise of third-generation Ryzen "Matisse" processors being backwards compatible with older Socket AM4 motherboards, going all the way back to the AMD 300-series chipset, with a simple BIOS update. To make the most out of Ryzen "Matisse"—namely, PCI-Express gen 4.0 connectivity and increased CPU/memory overclocking headroom, you're expected to use one of the latest motherboards that use the AMD X570 chipset. The X570 is an entirely different chip from X470 and X370. The older chipsets were supplied by ASMedia, and were rather slim in their downstream connectivity.

The X470 only puts out 8 PCIe gen 2.0 downstream lanes, for example. The X570 modernizes all I/O by putting out up to 16 PCIe gen 4.0 downstream lanes. This enables additional M.2 PCIe gen 4 slots on your motherboards for the latest SSDs featuring PCIe gen 4 support and creates room for many new bandwidth-hungry onboard devices, such as 10 GbE adapters, next-generation Thunderbolt, 802.11ax controllers, etc. Along with the "Matisse" SoC, the X570 also puts out a number of 10 Gbps USB 3.1 gen 2 ports. Motherboards based on X570 also implement modern network connectivity options, such as 2.5 GbE and 802.11ax WLAN.

Given there are highly capable motherboards based on the B550 chipset with serious VRM solutions and high-end connectivity, it's good enough for any Ryzen 3000XT series processor, including the 3900XT. The B550 chipset also offers multi-GPU support. Your choice between the B550 and X570 should hence boil down to whether you plan to have more than one M.2 NVMe SSD that can take advantage of PCI-Express gen 4.0, or an NVMe RAID setup of 2–3 PCIe gen 4.0-capable M.2 SSDs. Serious overclockers should still consider the X570 since the most beastly VRM setups are still found on boards such as the MSI MEG X570 GODLIKE, ASUS ROG Crosshair VII Formula, and GIGABYTE X570 AORUS Xtreme.

AMD StoreMI 2.0 Technology

AMD today is also debuting the second generation StoreMI technology, a value addition to its Socket AM4, TR4, and sTRX4 platforms. StoreMI is a free software for AMD users which allows you to build volumes that span across multiple storage devices, such as SSDs and HDDs. Depending on the "heat" (frequency of access) of the data, the software decides what data to store in the fastest media. Unlike the original StoreMI technology that debuted with AMD's 400-series chipset, StoreMI 2.0 is an in-house development by AMD and improves on an important front—the software doesn't physically move data between various storage devices. Rather, depending on available space and heat, it copies data from the slower media to the faster one, and points the OS to the copy that's on the faster media. This way, there's no scope for data loss. AMD also redesigned the user interface.

Mar 10th, 2025 13:31 EDT

change timezone

Latest GPU Drivers

New Forum Posts

- AMD RX 9070 XT & RX 9070 non-XT thread (OC, undervolt, benchmarks, ...) (2)

- newegg ATX 3.1 PSU on Clearance and Free Fan (3)

- Nvidia's GPU market share hits 90% in Q4 2024 (gets closer to full monopoly) (770)

- AAF Optimus Modded Driver For Windows 10 & Windows 11 - Only for Realtek HDAUDIO Chips (375)

- RX 9070 availability (165)

- DTS DCH Driver for Realtek HDA [DTS:X APO4 + DTS Interactive] (2110)

- Zen6 is almost here ? (45)

- Gaming PC instabiliity (16)

- It's happening again, melting 12v high pwr connectors (1019)

- What's your latest tech purchase? (23269)

Popular Reviews

- Sapphire Radeon RX 9070 XT Nitro+ Review - Beating NVIDIA

- XFX Radeon RX 9070 XT Mercury OC Magnetic Air Review

- ASUS Radeon RX 9070 TUF OC Review

- MSI MAG B850 Tomahawk Max Wi-Fi Review

- NVIDIA GeForce RTX 5080 Founders Edition Review

- NVIDIA GeForce RTX 5070 Founders Edition Review

- Corsair Vengeance RGB CUDIMM DDR5-8800 48 GB CL42 Review

- AMD Ryzen 7 9800X3D Review - The Best Gaming Processor

- ASUS GeForce RTX 5070 Ti TUF OC Review

- MSI GeForce RTX 5070 Ti Gaming Trio OC+ Review

Controversial News Posts

- NVIDIA GeForce RTX 50 Cards Spotted with Missing ROPs, NVIDIA Confirms the Issue, Multiple Vendors Affected (513)

- AMD Plans Aggressive Price Competition with Radeon RX 9000 Series (277)

- AMD Radeon RX 9070 and 9070 XT Listed On Amazon - One Buyer Snags a Unit (261)

- AMD RDNA 4 and Radeon RX 9070 Series Unveiled: $549 & $599 (260)

- AMD Mentions Sub-$700 Pricing for Radeon RX 9070 GPU Series, Looks Like NV Minus $50 Again (248)

- NVIDIA Investigates GeForce RTX 50 Series "Blackwell" Black Screen and BSOD Issues (244)

- AMD Radeon RX 9070 and 9070 XT Official Performance Metrics Leaked, +42% 4K Performance Over Radeon RX 7900 GRE (195)

- AMD Radeon RX 9070-series Pricing Leaks Courtesy of MicroCenter (158)