Tuesday, July 6th 2021

Samsung 5 nm Node Struggles With Yields, Reports Indicate Less Than 50% Yielding

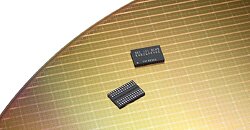

Semiconductor manufacturing is no easy task. Every company in that business knows that, and the hardships of silicon manufacturing have been felt by even the greatest players like Samsung and Intel. Today, according to the latest report from Business Korea, Samsung is again in trouble with its 5 nm node. It has been reported previously that Samsung is struggling with yields of its 5 nm node, however, we didn't know just how much until now. According to the sources over at Business Korea, Samsung's 5 nm semiconductor node is experiencing less than 50% yields. That means, for example, that out of 100 chips manufactured on a single silicon wafer, only half are functional. And that is not good at all.

Usually, for a node to go into high-volume manufacturing (HVM), the yielding rate needs to be around 95%. In case it is not at that level, manufacturing of that node is not very efficient and not very profitable. The V1 Line in Hwaseong, where this Samsung 5 nm is made, uses EUV tools to manufacture the new node. While the yields are currently below 50%, it is expected to improve as Samsung engineers tweak and tune the node and the tools that are running the facility. We can expect to hear more about the yields of this node in the coming months.

Sources:

Business Korea, via HardwareLuxx

Usually, for a node to go into high-volume manufacturing (HVM), the yielding rate needs to be around 95%. In case it is not at that level, manufacturing of that node is not very efficient and not very profitable. The V1 Line in Hwaseong, where this Samsung 5 nm is made, uses EUV tools to manufacture the new node. While the yields are currently below 50%, it is expected to improve as Samsung engineers tweak and tune the node and the tools that are running the facility. We can expect to hear more about the yields of this node in the coming months.

16 Comments on Samsung 5 nm Node Struggles With Yields, Reports Indicate Less Than 50% Yielding

www.techpowerup.com/283983/samsung-3-nm-gaafet-node-delayed-to-2024

50% YR would be horrible for something like Qualcomm's X60 at maybe ~30mm² but not too uncommon for some ~800mm² chip like next gens Nvidia Hopper.

I also don't think we are going to see mass-produced stackable DRAM anytime soon.

Bad news for Nvidia i guess if they to stick with Samsung for 40 series.

Tho 30 series problems with efficiency stem from G6X more than they do from Samsung.

The stuff so far is layers of 2D transistors being stacked, but the future is "3D" transistors, i.e. not flat transistors.

They could in turn be used in layered stacks.

Apparently FinFET is considered a 3D transistor, so I guess in a sense, we're already there.