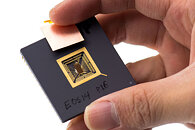

AMD, Samsung Partnership to See Variable Rate Shading, Ray Tracing on Exynos SoC

AMD at its Computex event shed some light on its IP partnership with Samsung. We already knew this was going to be a closer collaboration than most IP licensing deals, as AMD themselves announced this would be a semi-custom solution designed between both companies. AMD CEO Lisa Su described the technology to be embedded in the upcoming Samsung Exynos SoC as being based on RDNA2 - but this likely is just a marketing and clarity perspective on AMD's technology being implemented, since between the design of RDNA2 and the announcement of the Samsung partnership a lot of water has necessarily run under AMD's graphics IP bridge.

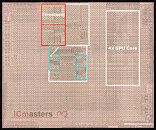

Lisa Su did however confirm that two key RDNA2 technologies will find their way into Samsung's Exynos: Variable Rate Shading (VRS) and Raytracing. This isn't he first time VRS has made an appearance on a mobile SoC - it's already been implemented by Qualcomm in the Adreno 660 GPU (part of the Snapdragon 888 SoC design). However, Raytracing does seem to be a first for the SoC market, and Samsung might just edge out competition in its time to market with this technology. more details will certainly be shared as we get closer to the fabled AMD-partnered Exynos release.

Lisa Su did however confirm that two key RDNA2 technologies will find their way into Samsung's Exynos: Variable Rate Shading (VRS) and Raytracing. This isn't he first time VRS has made an appearance on a mobile SoC - it's already been implemented by Qualcomm in the Adreno 660 GPU (part of the Snapdragon 888 SoC design). However, Raytracing does seem to be a first for the SoC market, and Samsung might just edge out competition in its time to market with this technology. more details will certainly be shared as we get closer to the fabled AMD-partnered Exynos release.