Samsung Successfully Completes 5nm EUV Development

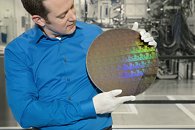

Samsung Electronics Co., Ltd., a world leader in advanced semiconductor technology, today announced that its 5-nanometer (nm) FinFET process technology is complete in its development and is now ready for customers' samples. By adding another cutting-edge node to its extreme ultraviolet (EUV)-based process offerings, Samsung is proving once again its leadership in the advanced foundry market.

Compared to 7 nm, Samsung's 5 nm FinFET process technology provides up to a 25 percent increase in logic area efficiency with 20 percent lower power consumption or 10 percent higher performance as a result of process improvement to enable us to have more innovative standard cell architecture. In addition to power performance area (PPA) improvements from 7 nm to 5 nm, customers can fully leverage Samsung's highly sophisticated EUV technology. Like its predecessor, 5 nm uses EUV lithography in metal layer patterning and reduces mask layers while providing better fidelity.

Compared to 7 nm, Samsung's 5 nm FinFET process technology provides up to a 25 percent increase in logic area efficiency with 20 percent lower power consumption or 10 percent higher performance as a result of process improvement to enable us to have more innovative standard cell architecture. In addition to power performance area (PPA) improvements from 7 nm to 5 nm, customers can fully leverage Samsung's highly sophisticated EUV technology. Like its predecessor, 5 nm uses EUV lithography in metal layer patterning and reduces mask layers while providing better fidelity.