Intel Core Ultra 2-series "Arrow Lake-S" Desktop Features 4 Xe-core iGPU, No Island Cores

Over the weekend, there have been a series of leaks from sources such as Golden Pig Upgrade, and High Yield YT, surrounding Intel's next-generation desktop processor, the Core Ultra 2-series "Arrow Lake-S." The lineup is likely to continue the new client processor naming scheme Intel introduced with the Core Ultra 1-series "Meteor Lake" on the mobile platform. "Arrow Lake-S" is rumored to debut the new Socket LGA1851, which retains cooler-compatibility with LGA1700. Although Intel has nucleated all I/O functions of the traditional PCH to "Meteor Lake," making it a single-chip solution on the mobile platform; and although the mobile "Arrow Lake" will continue to be single-chip; the desktop "Arrow Lake-S" will be a 2-chip solution. This is mainly because the desktop platform demands a lot more PCIe lanes, for a larger number of NVMe storage devices, or high bandwidth devices such as Thunderbolt and USB4 hubs, etc.

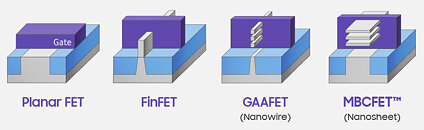

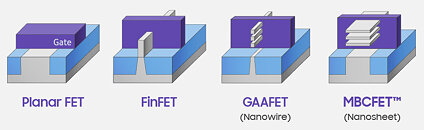

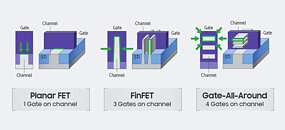

Another key finding in this latest series of leaks, is that unlike "Meteor Lake," the desktop "Arrow Lake-S" will do away with low-power island E-cores located in the SoC tile of the processor. All CPU cores are located in the Compute tile, which is expected to be built in the Intel 20A foundry node—the company's first node to implement GAAFETs (nanosheets), with backside power delivery; as well as an advanced 2nd generation EUV lithography. Intel's 1st Gen EUV is used on the current FinFET-based Intel 4 and Intel 3 foundry nodes.

Another key finding in this latest series of leaks, is that unlike "Meteor Lake," the desktop "Arrow Lake-S" will do away with low-power island E-cores located in the SoC tile of the processor. All CPU cores are located in the Compute tile, which is expected to be built in the Intel 20A foundry node—the company's first node to implement GAAFETs (nanosheets), with backside power delivery; as well as an advanced 2nd generation EUV lithography. Intel's 1st Gen EUV is used on the current FinFET-based Intel 4 and Intel 3 foundry nodes.